# Snubber Circuits For Power Electronics

## **Rudy Severns**

# Snubber Circuits For Power Electronics

Rudy Severns

## Copyright © 2008 Rudolf Severns

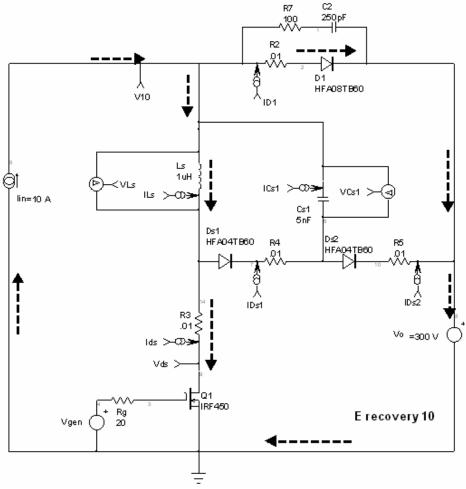

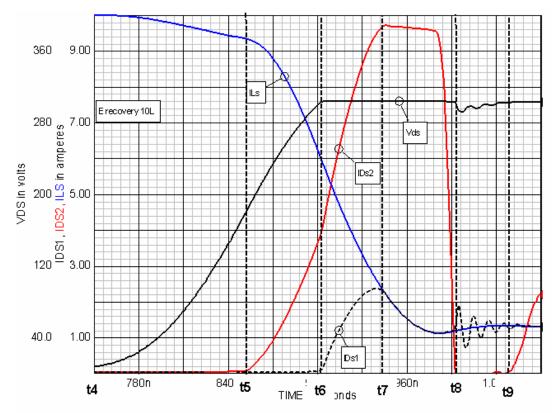

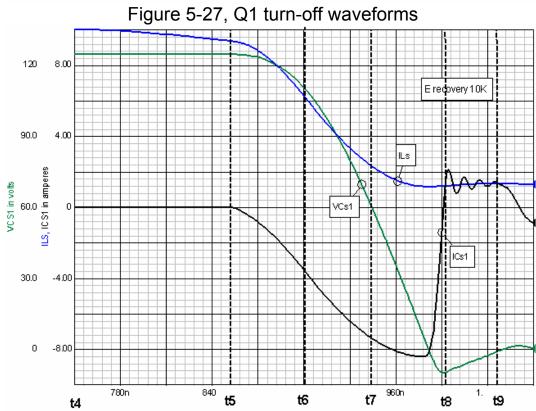

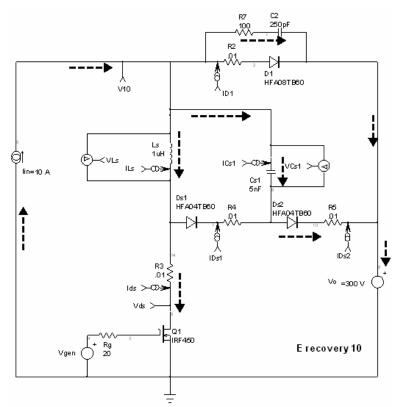

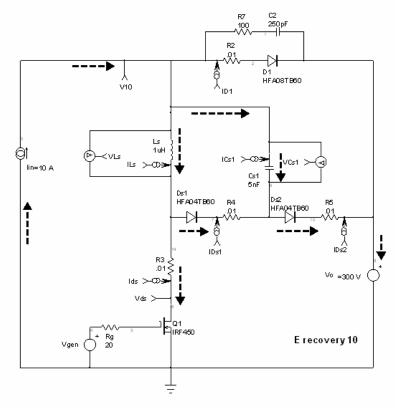

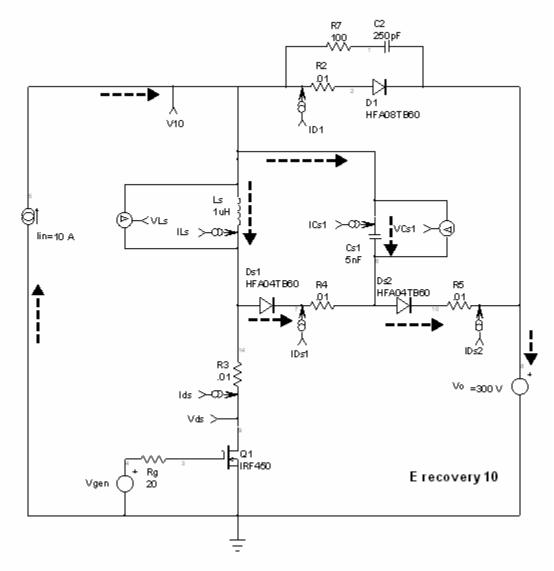

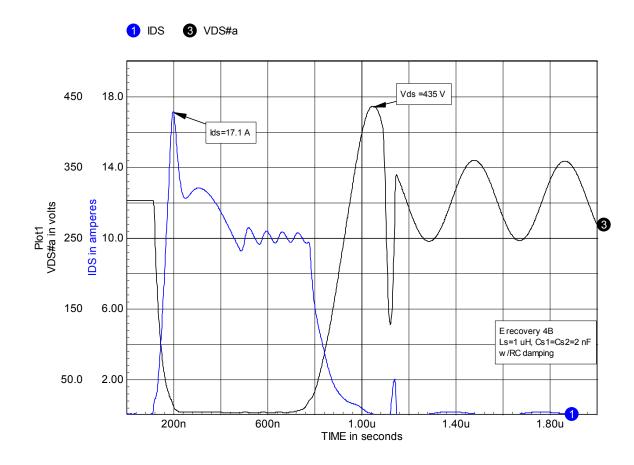

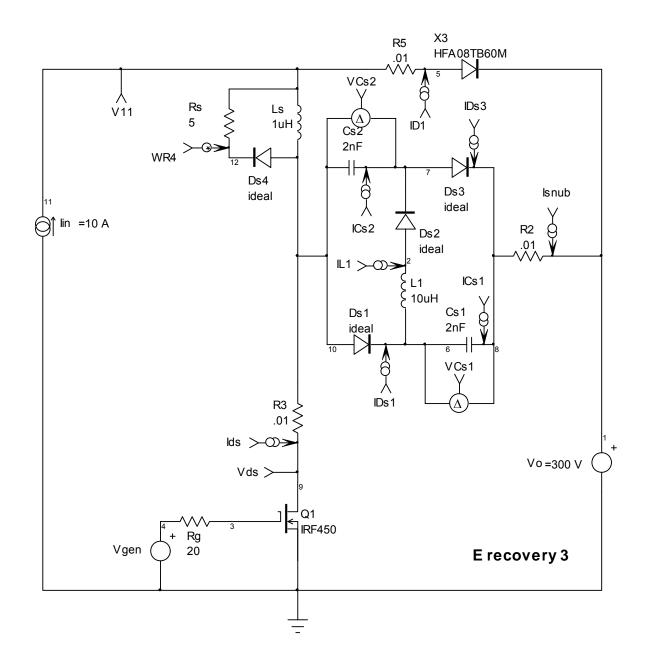

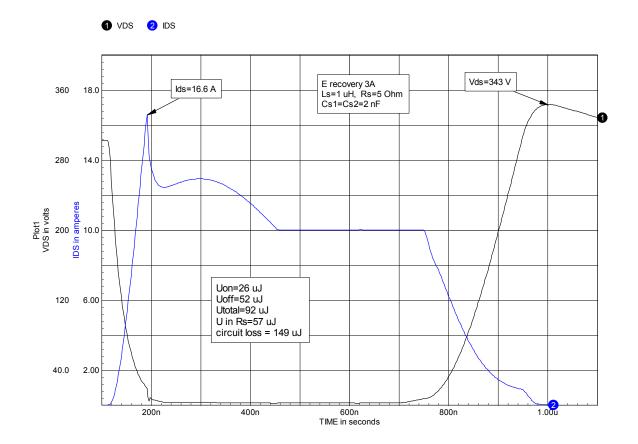

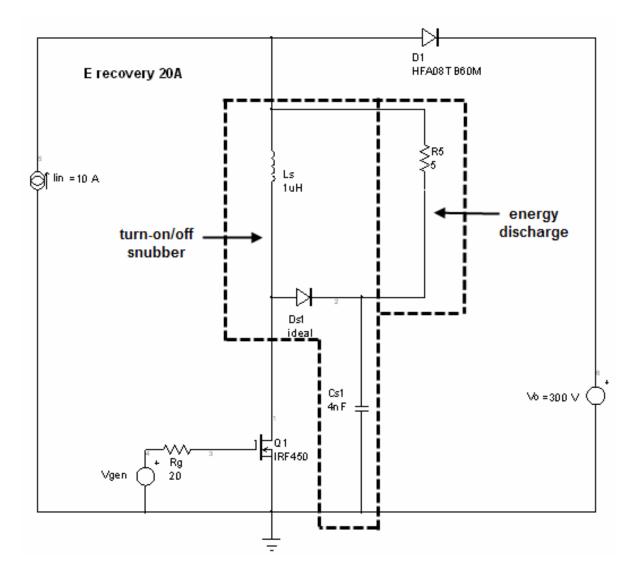

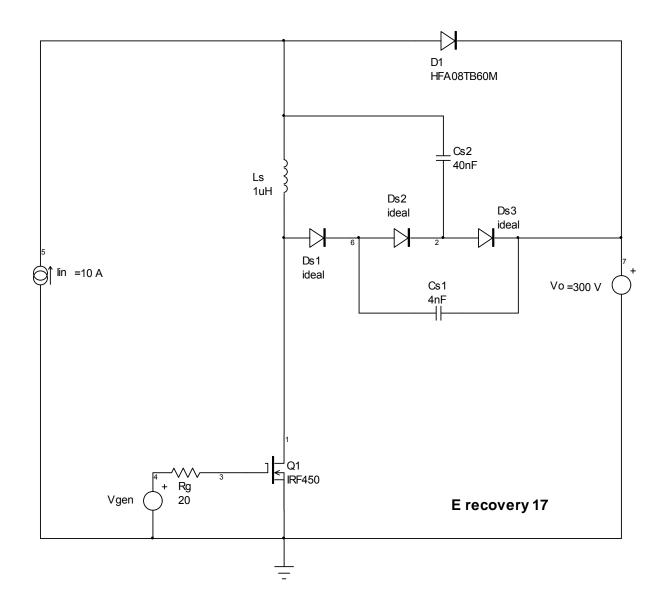

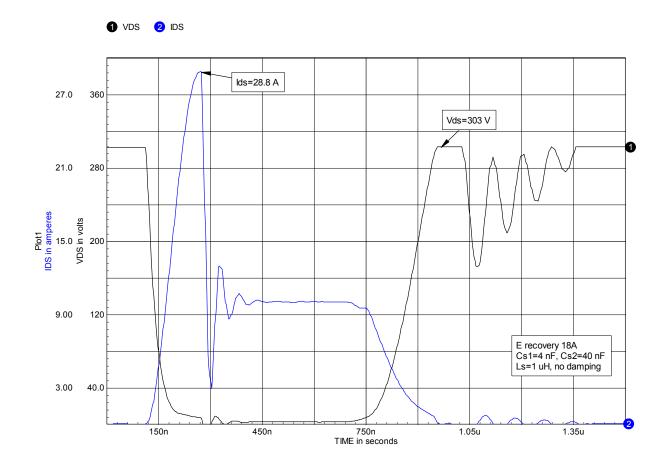

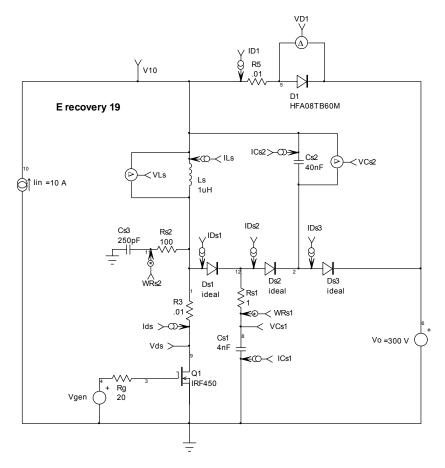

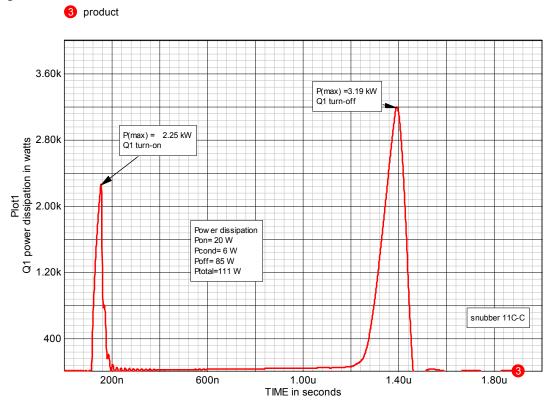

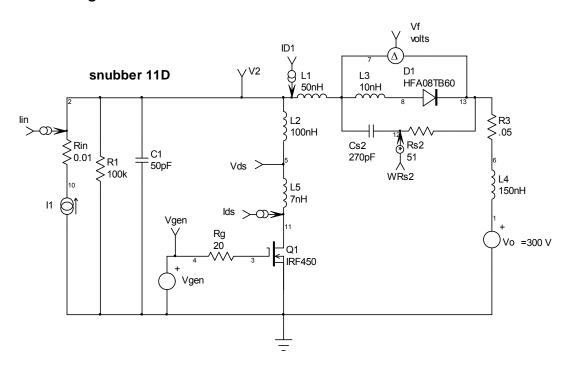

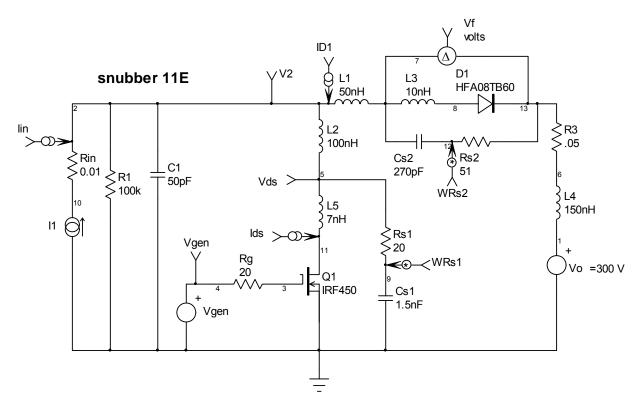

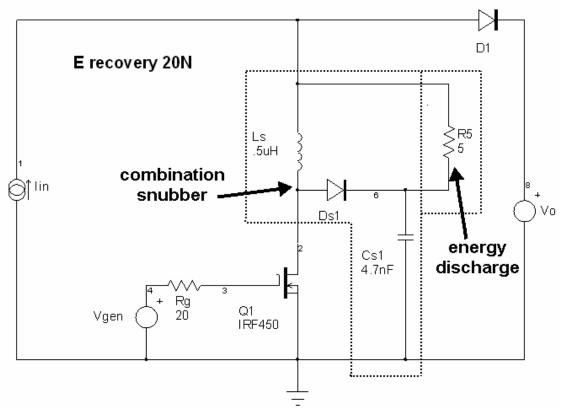

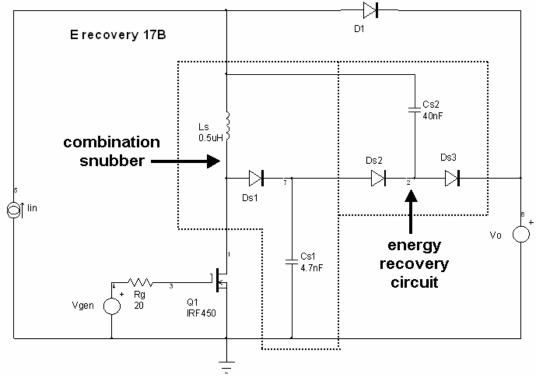

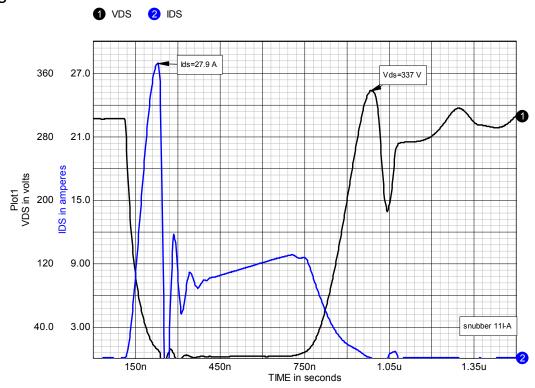

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, mechanical, photo-copying, recording or otherwise, without prior written permission of Rudolf Severns.

#### Legal notice:

Great effort has been made to make the material presented in this book as accurate as possible. However, the author and publisher assume no responsibility or liability whatsoever on behalf of any Purchaser or Reader of these materials. It is the responsibility of the user to exercise good engineering judgment when using this material.

#### A note from the author.

Preparing a book like this takes well over 1000 hours of effort and a substantial investment by the author and publisher. Hopefully, this book will prove to be a useful contribution to the power electronics art. When such books are successful and provide some reasonable return to their authors, there is motivation to write more such books on other important subjects. The result is of benefit to all in our profession. Honesty is a fundamental requirement for any professional engineer and is expected of those in the profession or training for it. Your help is requested in not making copies of this work and distributing it to others or in accepting any such copy.

## **Table of contents**

| PREFACE                                          | 7        |

|--------------------------------------------------|----------|

| ACKNOWLEDGEMENT                                  | 11       |

| CHAPTER 1                                        | 13       |

| An Overview Of Snubbers                          | 13       |

| What is a snubber?                               | 21       |

| Classifying snubbers                             | 22       |

| Snubber trade-offs                               | 24       |

| CHAPTER 2                                        | 25       |

| Things You Need To Know About Switches           | 25       |

| The ideal switch                                 | 25       |

| A generalized switch concept                     | 27       |

| Real switches                                    | 27       |

| Switch operating quadrant The load-line concept  | 30<br>31 |

| SOA concept                                      | 31       |

| Derating and SOA                                 | 34       |

| Switching scenarios                              | 35       |

| Resistive load switching                         | 35       |

| Clamped inductive switching                      | 37       |

| Unclamped inductive switching                    | 45       |

| Capacitive switching                             | 48       |

| Switching with real loads                        | 51       |

| Effect of parasitics on circuit waveforms        | 52       |

| Unintentional overlapping conduction in switches | 56       |

| Lack of desired overlapping conduction           | 60       |

| CHAPTER 3                                        | 61       |

| RC -snubbers                                     | 61       |

| Examples of RC-snubber use                       | 61       |

| A closer look at RC-snubber behavior             | 69       |

| Finding the optimum value for Rs                 | 72       |

| Choosing Cs A design example                     | 76<br>80 |

| CHAPTER 4                                        | 87       |

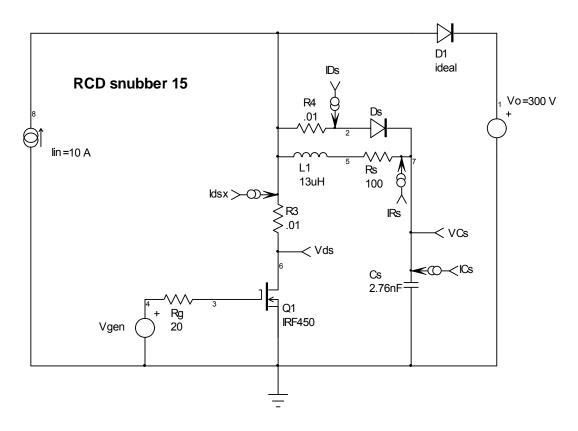

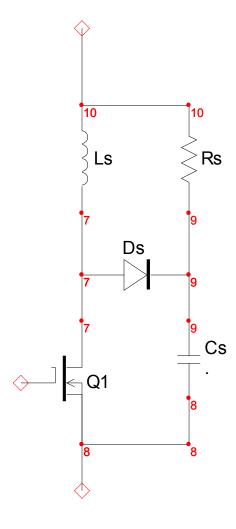

| Dissipative RLC-diode snubbers                   | 87       |

| Basic circuit                                    | 88       |

| A Turn-off snubber                               | 90       |

| Parasitic inductance and the turn-off snubber    | 102      |

| The turn-on snubber                              | 104      |

| Turn-on snubber with a real diode                | 112      |

| The combination snubber                                         | 118        |

|-----------------------------------------------------------------|------------|

| A simplified combination snubber                                | 122        |

| Waveform discontinuities                                        | 126        |

| Choosing the initial snubber component values                   | 128        |

| Snubber interactions                                            | 136        |

| Non-linear Ls and/or Cs                                         | 147        |

| CHAPTER 5                                                       | 151        |

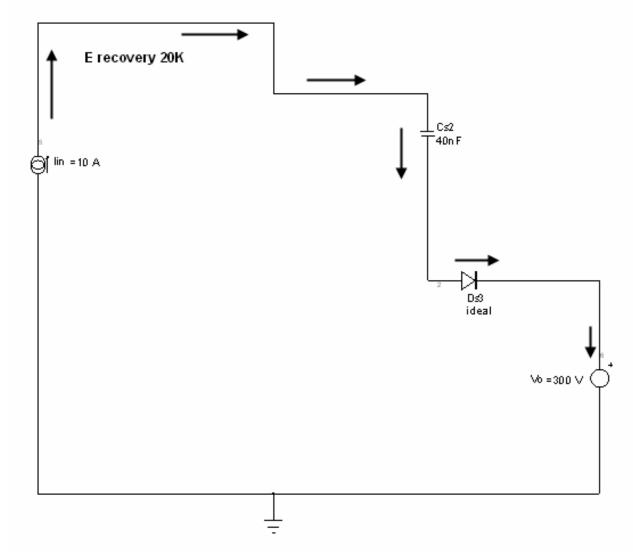

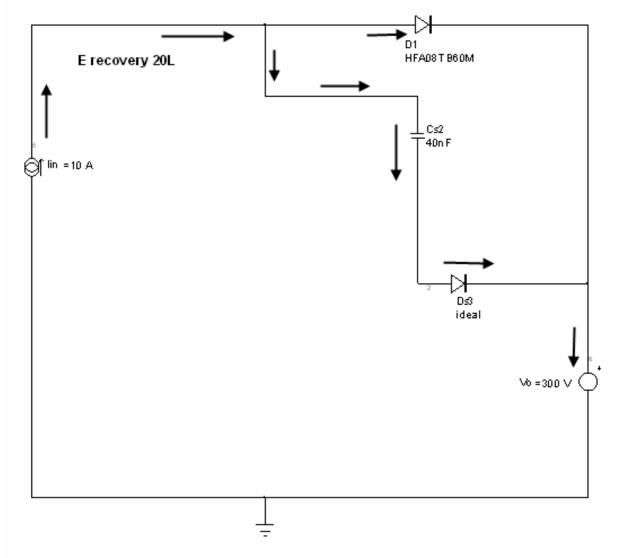

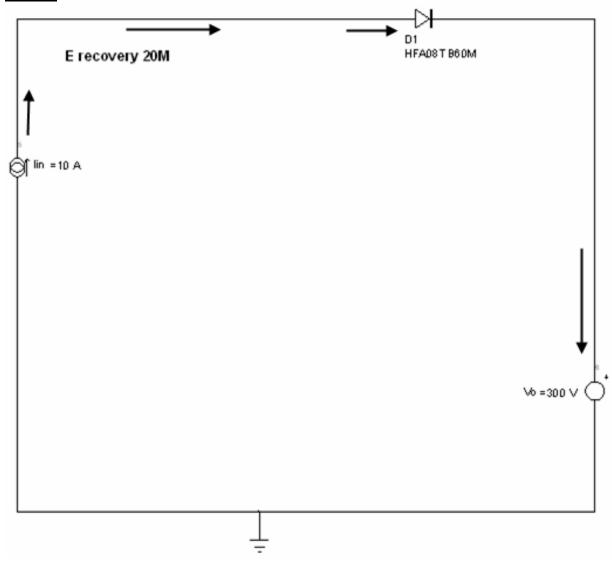

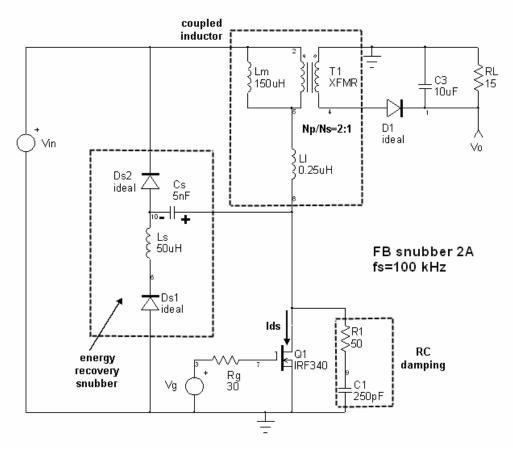

| Energy recovery snubbers                                        | 151        |

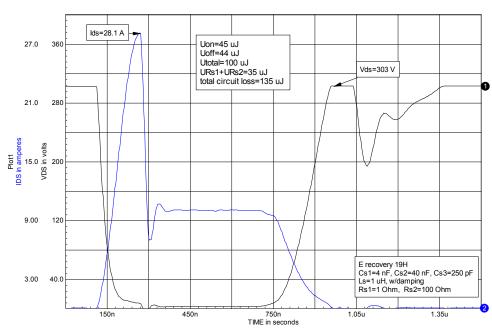

| A turn-off snubber example                                      | 152        |

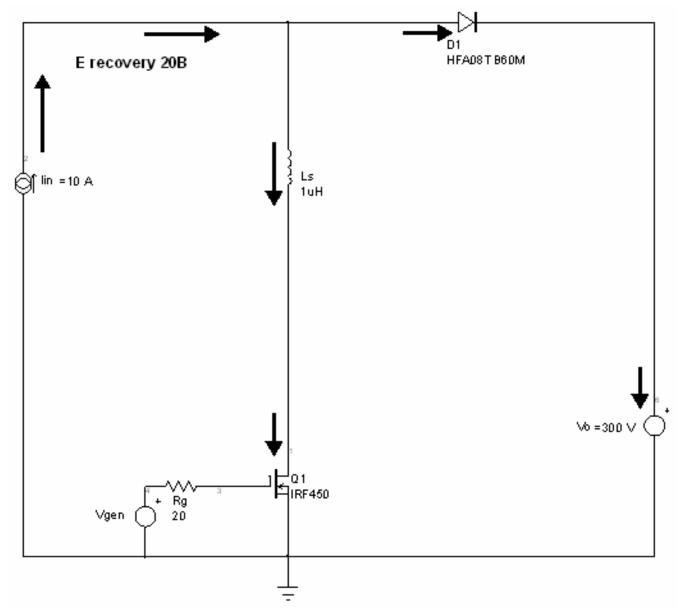

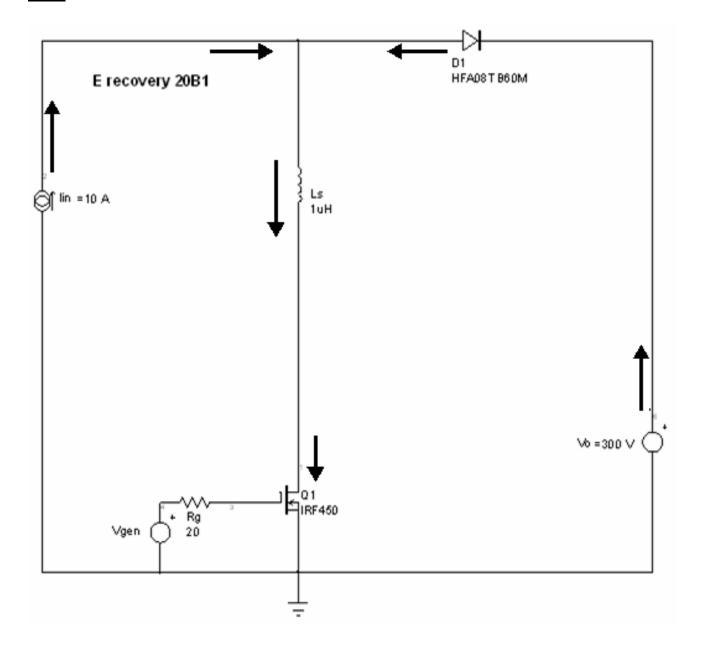

| Turn-on snubber example 1                                       | 164        |

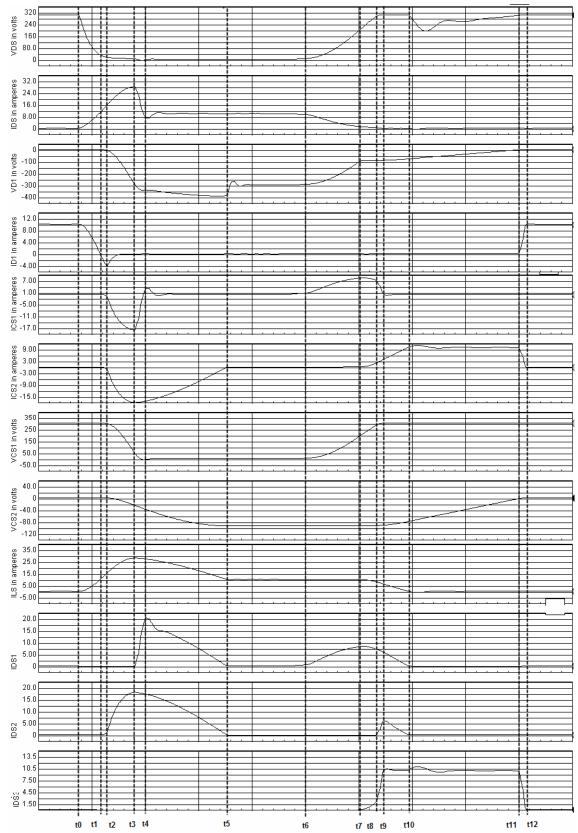

| Turn-on snubber example 2                                       | 184        |

| Combination energy recovery snubbers                            | 189        |

| Combination snubber example 1 Combination snubber example 2     | 191<br>193 |

| A flyback converter snubber                                     | 215        |

| Energy recovery snubbers for bridge connections                 | 222        |

| CHAPTER 6                                                       | 225        |

| Component selection and circuit layout                          | 225        |

| Diode selection                                                 | 225        |

| Ls design                                                       | 228        |

| Cs selection                                                    | 231        |

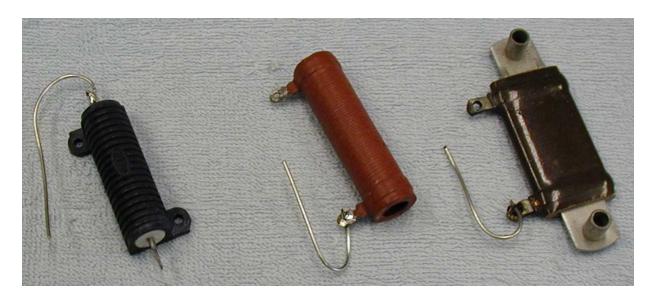

| Rs selection                                                    | 235        |

| Effect of parasitic L on snubber behavior                       | 239        |

| Package and layout inductance                                   | 243        |

| Comments on measurements                                        | 246        |

| One final reminder                                              | 252        |

| CHAPTER 7                                                       | 253        |

| Bare Bones Snubber Design                                       | 253        |

| Getting started                                                 | 254        |

| Example circuit                                                 | 255        |

| Circuit waveform and power loss survey                          | 257        |

| Example 1, an RC-snubber Example 2, another RC-snubber design   | 263<br>267 |

| Example 2, another RC-shubber design Example 3, more RC-shubber | 269        |

| Example 4,a turn-off RC-diode snubber                           | 272        |

| Example 5, a combination turn-on and turn-off snubber           | 279        |

| Example 6, an energy recovery snubber                           | 284        |

| Component values                                                | 291        |

| Summary                                                         | 294        |

| TECHNICAL LITERATURE BIBLIOGRAPHY                               | 295        |

| SNUBBER PATENT BIBLIOGRAPHY                                     | 339        |

| INDEX                                                           | 345        |

#### **Preface**

Switches play a major role in efficient power conversion and have a long history of use beginning with mechanical switches in the 1840's, vacuum and gas discharge devices during the first 60 years of the 20th century, through to today's wide variety of semiconductor devices. While switching device technology has changed dramatically over time, the need to use some form of auxiliary circuit to reduce switch stress and/or losses has been constant. In fact some of these auxiliary circuits, which are often referred to as "snubbers" or "switching aids", are the same today as they were in the 1850's, using the same components, in the same way, for the same reasons. Of course there have also been many new ideas as switch technology has evolved. Despite this long history, new and useful snubber variations still continue to appear. We still haven't invented everything when it comes to snubbers.

With so much activity over such a long period of time it's not surprising that there is a very extensive body of technical literature and patents on snubbers. As part of this book I have included an extensive bibliography (with over 500 entries!) but that's just a sample of the literature on the subject. Surprisingly, it does not appear that anyone has written a book on snubbers although there have been notes[388,441] applications multi-page Although electronics texts at least touch on the subject of snubbers, for the most part we still have to search through the literature to get detailed information on snubbers and their applications. This lack of a text which provides information on the design of snubbers and points the way to the wider literature is my motivation for creating this book. In the process I learned a very great deal which I wish I had known much earlier.

There is no pretence that this book is a complete source even though the subject is discussed at book length. Because of the breadth of the subject and the incredible variety of snubber circuits, all I've been able to do in the space available is to illustrate basic principles, describe the operation of typical examples, point out the similarities between many apparently different snubbers and give design guidance for some typical snubber circuits. To make the text more readable and accessible, I have elected to devote very little space to detailed analytic derivations of the equations describing circuit waveforms and operation. The literature is rich with such expositions and where appropriate I identify relevant references. This should allow the reader to gain a basic understanding of the operation of a particular snubber from the text and then proceed to related literature for more detailed information.

Besides space, there are other reasons for limiting the analytic discussion. As indicated in chapter 2, even for as simple a snubber as the RC-damping network, the analysis quickly becomes very complicated, especially when real circuit details, such as multiple distributed parasitics and the actual behavior of semiconductor devices during switching are included. From the point of view of designing and applying snubbers in the laboratory, often in some haste, it is much faster to use approximate expressions which will get you close to a solution and then adjust component values to optimize performance. I must admit that for years I have railed against this kind of cut-and-try design process in power electronics. In the case of snubbers however, I've had to admit that in the usual pressureproblem is discovered during cooker environment where a development and a quick fix is needed, this approximate approach works very well. More detailed analysis for the final product can (and should!) be done later. The literature is full of such analysis, particularly in papers with academic origins.

But when the pressure is on, even the relatively simple discussions of circuit operation which constitute most of this book, may be too involved. You may only want to know the time of day, not how to design the watch! To meet this need I have included a separate chapter entitled "Bare Bones Snubber Design". In that chapter I give only "do this, use this rule of thumb, etc" instructions with no justification. The idea is to use this information for a quick fix so you can get on with the project at hand. If you want to know more, that's what the rest of the book is for.

Throughout the text I have used SPICE modeling (Ispice by Intusoft) to explain and illustrate snubber operation. Circuit simulation has the advantage that you can idealize or simplify the circuit initially to demonstrate basic principles but then add more realistic components to better approximate the real world as your understanding increases. Fortunately, modern SPICE software does a very good job of simulating switch and snubber behavior. Of course simulation is never perfect, the actual circuit will always be somewhat different. But if you're careful to include reasonable values for parasitic elements, a design which looks good in simulation will usually work in the real circuit but will no doubt require some fine tuning to optimize. Fortunately many different free versions of SPICE are readily available to us. For the most part, even the student editions of these programs is perfectly adequate for snubber design. High priced, full featured versions are very nice when available but are <u>not</u> necessary.

One frustration for me has been what I've had to leave out. In particular I have not addressed the subject of "soft switching" in any detail. This is currently a subject of great interest and new developments but there is enough information on the subject that it deserves a volume of it's own. There is in fact no sharp distinction between snubbers and soft switching. Although they are not usually advertised as such, many "snubbers" are in fact a means to switch a device more "softly" and the transition from snubbers to soft-switching circuits is a gradual one. Many "soft-switching" circuits use principles common in snubbers with additional modification of the overall circuit added.

Chapter 1 gives an overview of snubbers, the variety of names for the same circuit, some terminology and a description of the many different uses for snubbers, along with an historical example dating from 1853.

A major theme of this book is how apparently different snubber circuits have common underlying principles. The differences are often superficial. That theme begins in chapter 2 and is continued throughout the book.

Chapter 2 is intended to show how switches behave and how they are used. There are many good texts<sup>[297]</sup> which go into the details of

semiconductor device operation, so that subject is treated very lightly. Instead, chapter 2 emphasizes the similarities between different devices and how they are used in switching power conversion, motor controls, etc. It also serves to introduce some additional terminology and operating modes which are to a large extent independent of the particular switching device employed. There is a discussion of parasitic elements (L and C) which are normal parts of any practical circuit and their effect on circuit behavior. This along with the discussion of switching different types of loads illustrates the motivation for using snubbers.

In chapter 3 we finally get down to talking about snubbers with the introduction of RC-damping networks. In chapter 4 diodes are added to the R, L and C components used in chapter 3 to create new families of snubbers with different properties. The snubbers in chapters 3 and 4 are dissipative in nature. While they may reduce dissipation in the switch, that energy is usually dissipated in the resistive part of the snubber instead.

In chapter 5 components are added to recover the energy which was dissipated in the snubbers of chapters 3 and 4 and put that energy to a useful purpose. This can result in a substantial improvement in overall circuit efficiency although there are practical limits which are also pointed out. The necessity of using RC-damping networks with most energy recovery snubbers is explained.

Chapter 6 treats the mundane but very important subjects of component selection, circuit layout and measurements. Chapter 7 is titled "Bare Bones Snubber Design". This chapter is strictly a cookbook with no justification for the instructions given. Justification is given at length in earlier chapters. It is intended for emergency use in the lab.

At the end of this book is a bibliography of books, technical articles and patents related to snubbers. Despite taking up more than 40 pages and over 500 entries, there is no pretence that this is a complete listing but it should be a reasonable sample of the literature over many years and provide an entrée to further research.

Rudy Severns, Cottage Grove, Oregon, April 2008

## **Acknowledgement**

This book has been a lot of fun to write with not too much pain but it would never have been done if Jerry Foutz hadn't nagged and encouraged me to do it. His unfailing support and very considerable efforts both as a reviewer and developing the means to disseminate the book were vital to the project. Without him, no book would have appeared, no matter how long I talked about it!

My special thanks to Pat Hamel for reviewing the book and finding many errors, some very egregious! I corrected these very quickly.

I also have to express my love and appreciation to my wife, Diana for her patience during the hundreds of hours it took to write this book. A whole lot of "honey do's" were seriously delayed which of course are now being carefully attended to.

## **Chapter 1**

#### **An Overview Of Snubbers**

Seldom can we clearly identify the originator of circuit ideas in widespread use over a long period of time. The capacitive turn-off snubber would surely seem to fall into that category but that turns out not to be the case. We know exactly where this snubber first appeared, at least in the literature.

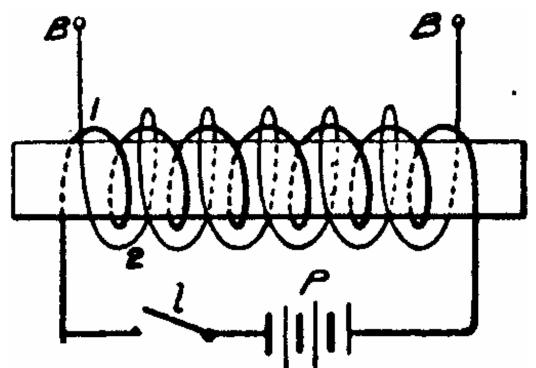

One of the key electrical discoveries of the 19<sup>th</sup> century was Faraday's invention of the induction coil which was immediately adopted by experimenters to investigate electrical phenomena.

Figure 1-1, equivalent circuit for an induction coil.

Figure 1-1 shows an equivalent circuit diagram. The idea was to create a spark across the secondary terminals when the primary switch was opened. When operating from a DC source it was recognized that nothing interesting happened until the switch in series

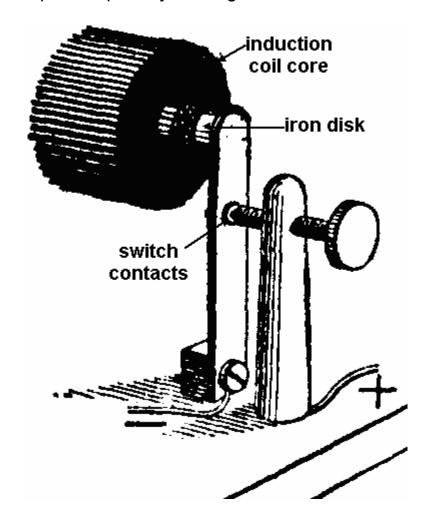

with the primary winding was closed for a period of time to store some energy in the inductance and then opened quickly. Early on it was realized that it was very helpful if the primary circuit could be opened and closed repetitively and this operation sustained for long periods of time. Many schemes were advanced to accomplish this. One popular way is shown in figure 1-2. The idea is that the switch contacts were on a leaf spring with an iron disk at one end. The disk was located close to the end of the induction coil core so that as the current built up in the primary winding a

Figure 1-2, induction coil switch arrangement.

point would be reached where the iron disk would be pulled towards the core, opening the contact and the primary circuit. After some period of time the energy stored in the core would dissipate (hopefully, in the secondary arc) reducing the holding force on the iron disk and allowing the spring action to reclose the contacts to

repeat the cycle. The circuit is self oscillating and represents a very early version of a self-oscillating DC-AC inverter operating in the continuous conduction mode (the coil energy did not quite go to zero before the spring closed the primary circuit for the next cycle, so there would be some current in the primary when the switch was reclosed). It is also an example of peak current mode control of the switch because the switch opens when an appropriate peak current is achieved. The leaf spring stiffness and spacing from the core were used to adjust the activation point.

As soon as the early workers had repetitive switching they immediately discovered the intrinsic problem of opening a switch with an inductive load. Early on an arc across the primary switch contacts was noticed when the switch opened. This arc had two effects, first it rapidly eroded the contacts. Second, some or even most of the available energy, intended for the secondary spark, was being consumed in the primary switch, which often heated rapidly. The switching loss was too high! Over 160 years ago the relationship between loss and switch behavior in an inductive circuit was recognized.

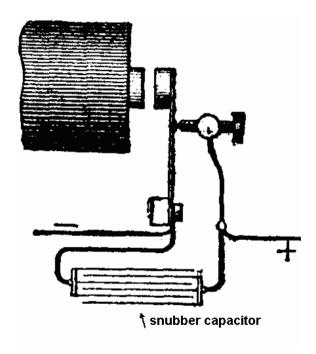

Figure 1-3, the capacitive snubber added across the switch contacts by Fizeau, 1853.

In 1853 Armand Fizeau [118] provided a solution for the problem. As shown in figure 1-3, Fizeau placed a capacitor across the contacts. When the switch turns off, the switch current is commutated to the capacitor but the voltage across the capacitor is very small because the switch has discharged it and only rises slowly as the integral of the current. The result is to allow the switch contacts to open with a very low voltage across them, minimizing the primary arc. This is exactly the same action we see in modern semiconductor capacitive turn-off snubbers. It is clear from Fizeau's paper that he understood exactly what the problem was and invented a solution. Of course the presence of a capacitor across the primary while the secondary was discharging led to the kind of ringing voltage waveform we often see associated with modern snubbers. Snubbers can perform very useful functions but almost always there is a price to pay in the "side effects" introduced by the snubber. We will see this recurrent theme in later chapters.

Because switching of inductive loads is intrinsic to most power conversion a great many schemes have been advanced for "commutation aids" - circuits which reduce the loss or stress on a switch while turning on or off. These range from a wide variety of snubber circuits, soft switching using resonant transitions, zero current switching (ZCS) resonant converters and ZCS and zero voltage switching (ZVS) quasi-resonant circuits. ZVS switching implies that at turn-on and/or turn-off the voltage across the switch is close to zero or at least small. There may however, be current flowing during the transition. ZCS switching implies that at turn-on and/or turn-off the current is very small. Both conditions can lead to significant reduction in switching loss.

ZVS and ZCS switching using resonant transitions is presently an active topic. The latest revival of interest is relatively recent and this technique is widely thought to represent something new. While certainly very useful, it's not new by any means. Resonant transition switching is an idea with a long history in power conversion.

In the early 1920's radio equipment began to be widely used in vehicles. Most of these early vehicles could only provide low voltage DC (6-24 V) power sources. Unfortunately the vacuum tube technology of the day required the use of DC voltages of 100 V or

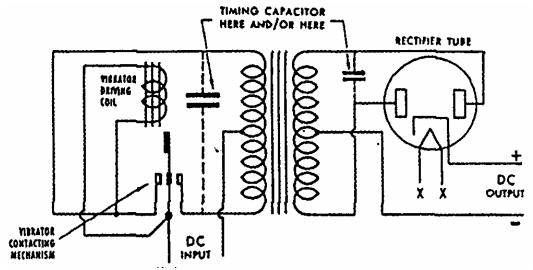

more. One of the most common means to provide high voltages was to employ a mechanical vibrator to chop the input DC to make AC, pass it through a step-up transformer, then rectify and filter it on the secondary. An example of such a DC-DC converter is given in figure 1-4. This figure was taken from the 1947 Mallory Handbook [276] but represents a technology that matured in the late 1920's and early 1930's.

Figure 1-4, example of a vibrator DC-DC converter.

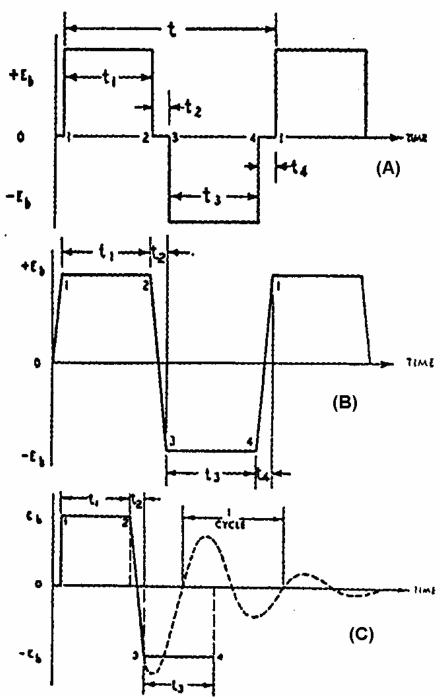

In figure 1-4 there is a capacitor (referred to as the "timing" capacitor) placed across either the primary or the secondary windings of the This capacitor, along with transformer leakage and magnetizing inductances, provided resonant transition switching that greatly extended the vibrator contact life. That this example exactly reproduces the modern resonant transition switching can be seen in Figure 1-5 which shows typical circuit waveforms [276] associated with figure 1-4. Figure 1-5C shows that the transition is the first part of a resonant ringing waveform. A deadtime (t<sub>2</sub> & t<sub>4</sub>) between the opening of one set of contacts and the closure of the other set, was deliberately introduced to allow for resonant transition switching. The discussion in the handbook goes on to point out the effects of too small and too large a deadtime. The length of the deadtime was controlled by the inertia of the reed, which had a small weight on it, and the spacing of the contacts. Obviously the concept of resonant transition switching was clearly understood 80 years ago!

Figure 1-5, switching waveforms associated with figure 1-4.

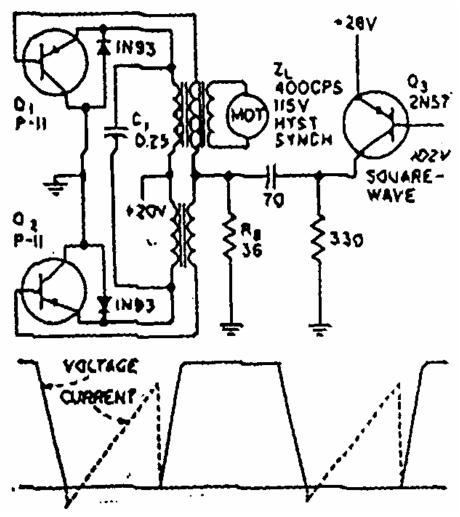

When power transistors became available in the mid-1950's, vibrators began to be replaced with transistors with anti-parallel diodes as shown in Figure 1-6 (along with representative current and voltage waveforms). Note that the switch current was deliberately made negative at switch turn-on (an inductive load), with the current flowing through the anti-parallel diode to provide zero-voltage turn-on.

Figure 1-6, DC-AC inverter with soft switching.

A capacitor was used along with the transformer inductances to provide resonant transition switching. These Figures are taken from a 1958 Electronics magazine article<sup>[53]</sup> that specifically addresses the issue of increasing switching efficiency by using what we now refer to as "soft-switching".

Vibrator and transistor inverters were not the only applications for soft switching. Beginning the 1930's inverters using thyratrons, grid controlled mercury arc tubes and ignitrons were in common use and also required switch commutation aids. When thyristors become available in the late 1950's, the earlier technology from thyratrons, ignitrons and magnetic amplifiers was adapted for the new devices. Over a period of 50 years almost every conceivable commutation circuit was examined. Commutation using an auxiliary switch, of

which much has recently been written, is a very old trick that has been well explored in an amazing variety of variations beginning more than 70 years ago.

We can extend the term "soft switching" to cover a wide variety of snubber circuits which are intended to reduce switching loss. For example the conventional RC-diode snubbers can be designed to provide very soft, low-loss turn-off by selecting an appropriate capacitor value. An analysis of a typical soft switching circuit, such as the phase-shifted bridge circuit with a primary inductor, shows that at turn-off the behavior is exactly the same as a normal RC-diode snubber and the turn-off loss in the switches is described by the same equations.

The need for commutation aids when using switches with inductive loads has been obvious from the beginning. If nothing else the arcing of the contacts or the failure of the switches would bring this to the attention of the experimenter. This requirement drove the invention of most of the techniques we now use.

In some ways a mechanical switch is more difficult to protect than a typical semiconductor switch. A mechanical switch has a voltage breakdown problem not normally seen in electronic switches. The breakdown voltage of the gap between the contacts depends on the spacing between the contacts (among other things). When the switch first starts to open, the spacing is very small and the breakdown voltage low. As the switch contacts open, the breakdown voltage capability increases rapidly but you still have the initial vulnerability because the arc can be sustained as the contacts open. To minimize arcing, it is necessary to have a capacitor large enough that the rate of rise of voltage across the contacts is slower than the rate of rise of the breakdown voltage capability. This subtlety was appreciated 150 years ago.

The point of this history lesson has been to show that the problems arising from switching an inductive load come from the nature of the load and the desire to combine it with a switch. Problems arise because we are "switching" and are not necessarily unique to a particular type of switch. Because of the universality of these problems, snubber techniques have a long history in power

conversion with all types of switches. Of course each switch type has it's own set of limitations which must be taken into account when designing a snubber but the basic principles are relatively independent of the switch type.

#### What is a snubber?

That sounds like a very simple question but unfortunately there is no simple answer. The reason is that circuits referred to as "snubbers" often perform quite different functions. The term "snubber" appears to have come down to us from a damping element in a mechanical system with masses and springs. The purpose was (and still is for that matter) to damp mechanical oscillations. The common automotive shock absorber is a form of mechanical snubber.

For electrical circuit snubbers one definition might be:

A snubber is a network that alters the voltage and/or current waveforms of a switch during turn-on and turn-off.

While probably true, this definition is so general as to be of very limited use.

Rather than trying to work up some contorted universal definition to cover every case, it's easier to simply list typical applications and extend that list as we think up new ones. Here are some:

- peak voltage limiting

- peak current limiting

- dV/dt limiting

- dl/dt limiting

- load-line shaping to stay within the safe operating are (SOA) boundaries

- improve circuit reliability through reduced electrical and/or thermal stress.

- switching loss reduction

- transfer of switching loss from the switch to a resistor or a useful load

- EMI reduction

- voltage sharing in series devices

- current sharing in parallel devices

- increasing the power obtainable from a given device or devices in a given application

- extension of switch service life

#### Following comments apply to snubbers:

- A snubber controls or manages energy on a transient basis during and immediately after switching transitions.

- The use of a snubber can greatly increase the power handling capability of a given device or increase it's reliability or both.

- Snubbers are sometimes referred to as "switching" or "commutation" aids.

#### **Classifying snubbers**

There have been many attempts to derive universal classification schemes<sup>[106]</sup> for snubbers. The problem is the many different functions performed by circuits we call "*snubbers*". In general such schemes haven't been particularly useful but for the purposes of this book, we will group snubbers with similar characteristics. None of these distinctions are very rigorous but are convenient to subdivide the discussion:

#### Passive.

Snubbers made up of lumped linear network elements, i.e. resistors, capacitors and/or inductors.

#### Active-lossy.

These are networks which use non-linear or active devices such as diodes or switches in addition to resistors, inductors and/or capacitors. This class of network dissipates a majority of the switching loss but usually in a resistor rather than in the switching device.

#### Active-low loss.

In this type of snubber circuit the energy which would normally be lost in the snubber resistor(s) is delivered either to the input source or to some useful load.

#### Non-polarized.

These are networks which have no preferred polarization, i.e. they can be installed in the circuit without regard to polarity. An example would be a simple series R-C damping network.

#### Polarized.

Most snubber networks using active devices can be installed in the circuit with only a given polarity. At least in principle, almost any polarized snubber network can be made non-polarized by imbedding it in a diode bridge. This is similar to the 4-quadrant switches shown in figure 2-5 (see chapter 2). But in general most active snubbers have a defined polarity.

#### Soft switching

Conceptually, "Soft switching" is enabling the switch to turn on and/or off with either very low voltage across the switch or very low current through the switch. This can result in very low switching loss and stress. Many snubber circuits do provide varying degrees of soft switching but this term is usually reserved for circuits which use either resonant topologies or some form of resonant transition switching to control switch stress. While these approaches are very popular and useful techniques, they are beyond the scope of this book.

#### **Snubber trade-offs**

No matter how useful or interesting snubber circuits may be they still require design compromises between:

- cost

- complexity

- reliability

- loss

- circuit performance

To list just a few. Of course these trade-offs would apply to any electronic circuit. Snubbers are no different in this respect. There is one very important trade-off which is unique to snubbers and which we will see repeatedly in later chapters describing circuit operation:

In many, if not most, cases when a snubber is added to the circuit, in addition to alleviating one problem, some additional new stress will be introduced into the switch.

The benefits of the snubber must be traded against it's disadvantages by selecting component values which achieve the desired results while minimizing the undesired.

## Chapter 2

## Things You Need To Know About Switches

All switches have limitations such as peak voltage, peak and average current, power dissipation, switching speed, etc. Snubbers are used to improve the performance and reliability of switches imbedded in power circuits but to properly apply snubber techniques it is important to understand how switches themselves behave. This chapter is devoted to a review of switches. We are not going to go into the detailed behavior of each type of switch, but rather look at the general behavior shared by all switches. For specific semiconductor switches see the bibliography. The discussion by Mohan, Undeland and Robbins<sup>[296]</sup> is a particularly good one for semiconductor switches.

#### The ideal switch

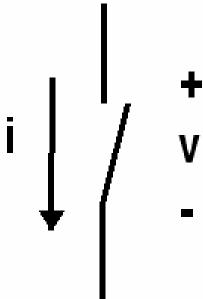

The simplest form of switch can be represented schematically as shown in figure 2-1.

Figure 2-1, representation of an ideal switch including current and voltage polarity conventions.

This is just a two terminal device which blocks current when open and conducts current when closed. An ideal switch, in the open or "off" state, will conduct no current with a voltage of either + or - polarity applied across the terminals. In the closed or "on" state, an ideal switch will conduct current in either direction but have no voltage drop across the terminals. In other words it is a bipolar device which presents an infinite impedance when off and zero impedance when on. This means there is no power dissipation in either state. A further property usually associated with an ideal switch is that the transitions from on-to-off and off-to-on are instantaneous. Ideally switching is accomplished with no power loss.

Power conversion circuits frequently require more than a simple SPST switch. More complex switching functions such as the SPDT switch shown in figure 2-2, can be implemented from combinations of SPST switches.

Figure 2-2, more complex switches are made up from combinations of simple switches.

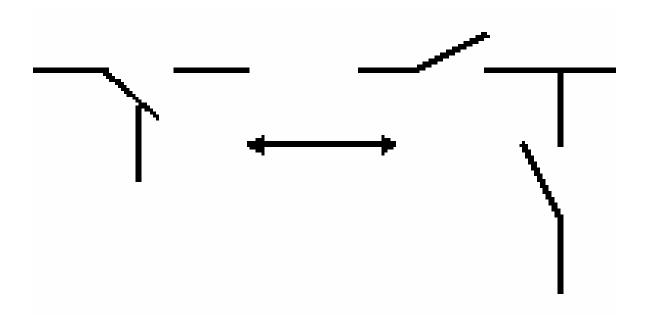

#### A generalized switch concept

In selecting devices to be used as switches we normally think in terms of some specific type of semiconductor device. A MOSFET or a thyristor for example. However, it is often more productive to think in terms of a more general form of switch: i.e. the device or circuit which performs the switching function may be composed of multiple semiconductors and other components such as capacitors, inductors and resistors, in a network. Examples of this might be a BJT combined with a snubber network as shown in figure 2-3. The result may be a more rugged and/or less expensive and/or more efficient switch. In many cases the most appropriate approach uses multiple devices working together to implement the desired switch function.

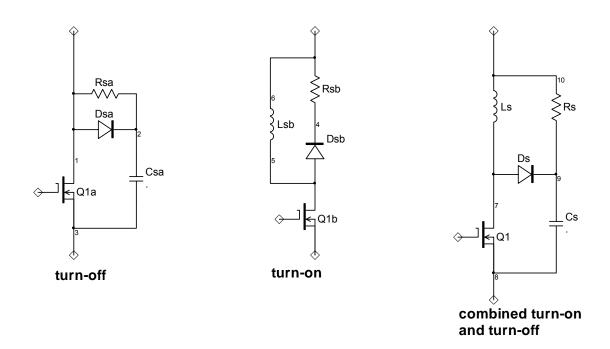

Figure 2-3, example of "switches" being implemented with a combination of a semiconductor devices and auxiliary components.

Switches are sometimes implemented by either the series or parallel combination of the same or different types of devices: a MOSFET in the emitter of a BJT for example. Many different combinations are seen in practice.

#### **Real switches**

Real switches take many forms: mechanical, vacuum tube, gas discharge or semiconductor. Although most of the techniques presented in this book can be applied to different kinds of switches we will limit our attention to semiconductor switches because they are

by far the most common type employed today. Semiconductors are of course not ideal devices and have many limitations:

- a. There will be a voltage drop across the device during conduction (on-state).

- b. There will be some current flow in the off-state.

- c. Transition times from on-to-off and off-to-on are finite and therefore lossy.

- d. Real switches have four states: on, off, transition from on-tooff and transition from off-to-on. In most cases the transitions will not be symmetrical.

All of these lead to power dissipation in the switch. In addition there are other limitations such as maximum blocking voltage, maximum conduction current, maximum dv/dt and di/dt rates, polarity of the conduction and blocking, instantaneous and average power dissipation, to name just a few. Snubber circuits are used to mitigate the consequences of non-ideal behavior in semiconductor switches.

Fortunately ideal switch behavior is usually not required. Take for example switch transition time or "switching time". In an ideal switch this time is zero (i.e. instantaneous). With power MOSFETs switching times of less than 1 nsec are possible, which is a pretty good approximation of instantaneous in most applications. However, because of interaction with other switches and elements in the circuit, such rapid transitions can lead to a host of problems, such as EMI, increased power loss in other devices, increased peak voltage and current stresses and inappropriate turn-on of other switches in the circuit. In practice what we really want is to be able to control both switching time and the instantaneous voltage and current waveforms during the transitions to suit the application. In many applications it is not necessary to block bipolar voltages or conduct bipolar currents. Unipolar capability is sufficient.

The point here is don't try to provide performance you don't need for the application!

Another important switching device characteristic is how the switch is commutated (turned on and off). There are many kinds of semiconductor switches with different commutation requirements. These are summarized in table 2-1.

Table 2-1 Semiconductors and how they are commutated

| Device           | Turn-on  | Turn-off |

|------------------|----------|----------|

| diodes           | circuit  | circuit  |

| thyristor family | external | circuit  |

| BJT, MOSFET      | external | external |

| IGBT, GTO, MCT   |          |          |

The following examples illustrate the point being made in table 2-1. A diode is a two-terminal device that is in conduction as long as it is forward biased. It turns off only when the terminal voltage reverses and the charge within the device allowed to dissipate. Turn-on and turn-off are controlled by the circuit in which the diode is imbedded.

Some devices, such as the thyristor family, can be commanded to turn on by an external pulse applied to the gate. However, to turn off and be able to block voltage, the current in these devices must first go to zero and remain there for a appreciable length of time, often many µsec. With these devices turn-on is via a gate pulse but turn-off is controlled by the circuit in which they are imbedded. There will frequently be auxiliary switches and associated networks to force turn-off.

Commutation of devices like the BJT, MOSFET or IGBT is in response to an external signal for both turn-on and turn-off. One caution however, some devices, like the IGBT, may be driven into a mode where they will not turn-off on command.

A common problem is the unintended turn-on by circuit waveforms, independent of the desired gating signal. Snubbers can play an important role in avoiding these undesired commutations.

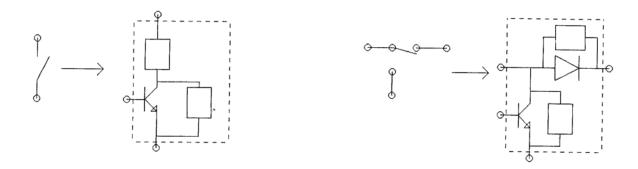

#### **Switch operating quadrant**

We can segregate switches by the polarity of the voltages and currents they can conduct or block. The operating quadrant of a switch can be defined using figure 2-4.

Figure 2-4, operating quadrant.

The circuit application determines the quadrant capabilities required in the switches. Figure 2-5 gives examples of 1, 2 and 4-quadrant switches.

|                  | ·                  |       | T          |             |

|------------------|--------------------|-------|------------|-------------|

| block<br>voltage | conduct<br>current | quads | device     |             |

| uni              | uni                | ]     | -D+        | <b>←</b> →  |

| bi               | uni                | 2     | -X         | <del></del> |

| uni              | bi                 | 2     | K          |             |

| bi               | bi ^               | 4     | $\Diamond$ |             |

Figure 2-5, examples of 1, 2 and 4-quadrant switches.

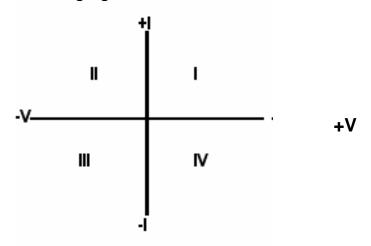

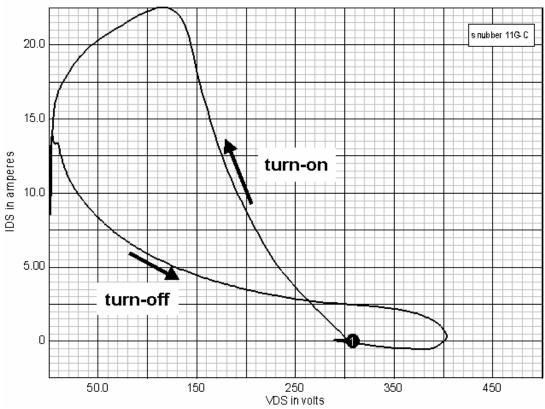

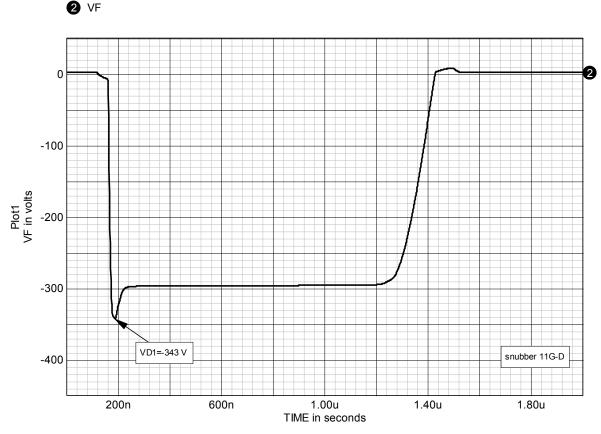

#### The load-line concept

A switch will assume several states during an operating cycle, on, transition to off, off, transition to on, which are repeated each cycle. Both the current through the switch (I) and the voltage across the switch (V) will vary during an operating cycle. The instantaneous values of V and I can be visualized by looking at their waveforms on an oscilloscope. But there is another very useful way to visualize switch operation over a switching cycle. Instead of plotting V and I separately against time, we can plot them against each other on a V-I diagram like that shown in figure 2-6 which shows the instantaneous V and I at each point during the switching cycle. This is referred to as a "load-line diagram".

Figure 2-6, an example of a load-line diagram.

The dashed lines represent lines of constant power dissipation, i.e. the product of the instantaneous V and I. This picture allows us to see

at a glance the stresses on the switch due to it's interaction with the circuit and also the effect of a snubber if present. The solid lines on the diagram represent a possible switching scenario. The arrows on the solid line indicate the direction of change as time progresses during the cycle. At point 1 the switch is off. At turn-on the trace proceeds to point 2 which is the completion of the on-transition. The trace between points 2 and 3 represent a possible change in current during the on-state. At turn-off, the trace transitions from point 3 back to point 1, the off-state. The load-line diagram is an important tool for illustrating the behavior of a snubber circuit.

Take special note of the relationship between the constant power lines and the load-line. For example, as we proceed from point 1 to point 2, the instantaneous power increases until it reaches a maximum of about 450 W in this example. Beyond that point the power decreases. The maximum power point, is a point of high stress on the switch, with both high voltage and high current present simultaneously. One of the many uses for snubbers is to modify the load-line to minimize this peak stress. High stress can also occur on the turn-off part of the load line.

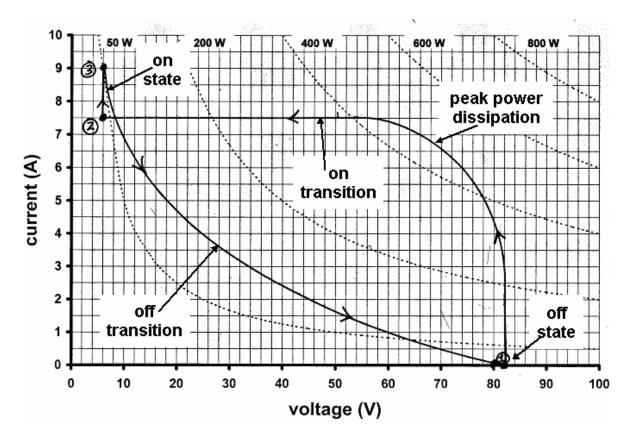

#### **SOA** concept

All semiconductor devices have V, I and instantaneous V\*I product limitations which must not be exceeded if reliable operation is to be achieved. One way to show these limitations for a given device is to plot the limits as boundaries on a V-I diagram and then plot the load-line to see if it lies within these boundaries.

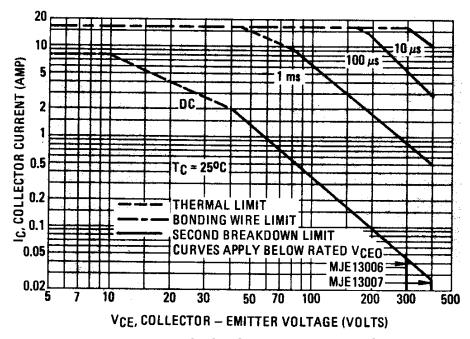

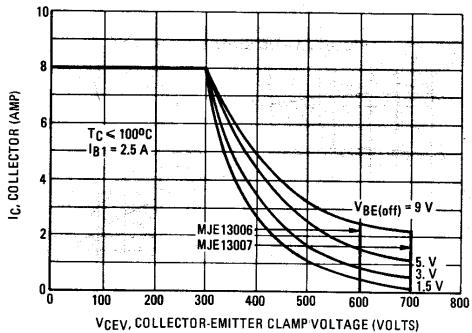

An example of a pair of BJT safe operating area (SOA) graphs is given in figures 2-7 and 2-8. In operation it is important that the load-line lie entirely within the SOA. In BJT's the SOA differs between the off, transition to on and on operation versus the on, transition to off and off operation. This is the difference between "forward biased" and "reversed bias" operation. That's why there are two different SOA graphs for a single device. To use these two graphs you need to plot that portion of the load-line corresponding to turn-on on the graph in figure 2-7 and plot the portion of the load-line corresponding to turn-off on the graph in figure 2-8. An important application for

snubbers is to assure that the load-line remains within the SOA boundaries under all operating conditions that the converter is expected to survive.

Figure 2-7, Forward biased Safe Operating Area for a MJE13006-7 BJT.

Figure 2-8, Reverse biased Safe Operating Area for a MJE13006-7 BJT.

#### **Derating and SOA**

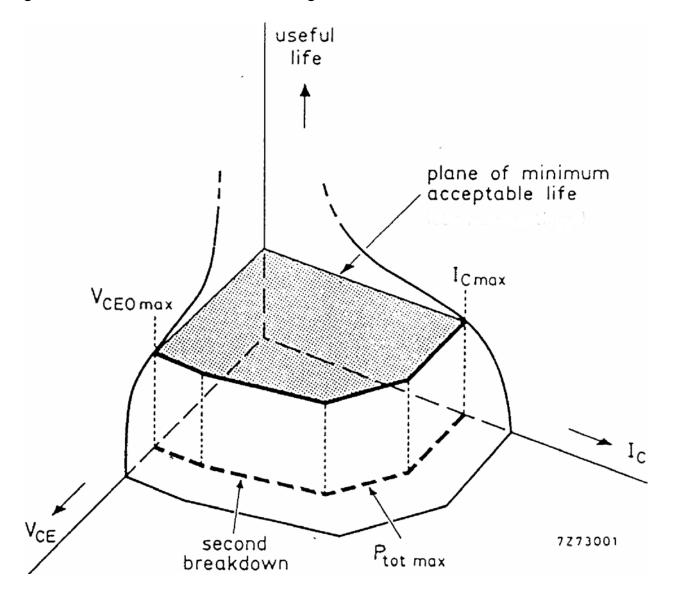

It is normal practice to derate a semiconductor from the manufacturers maximum ratings for voltage, current, V\*I product and junction temperature to increase reliability and life expectancy in actual circuit use. We can extend the concept of SOA to include the gain in useful life as illustrated in figure 2-9.

Figure 2-9, the extended SOA graph.

In addition to the limits shown on the SOA graph, some semiconductors also have limitations on dV/dt and dl/dt. This is characteristic of the thyristor family of devices. Excessive dV/dt can

lead to spurious turn-on and excessive dI/dt can lead to current crowding within the device die and lead to failure. These problems can be addressed by limiting the minimum switching time, choice of circuit and by using snubbers.

#### **Switching scenarios**

The circuits in which switches are used present different kinds of loads. The load may be resistive, inductive, capacitive or, more likely, some combination of all three. The nature of the load has a profound effect on the load-line and the choice of snubber circuit. For simplicity we will examine each case separately. Later we will combine the loads.

#### Resistive load switching

A resistive load is one of the simplest. Figure 2-10 shows a switching circuit with a resistive load.

Figure 2-10, Resistive load switching example.

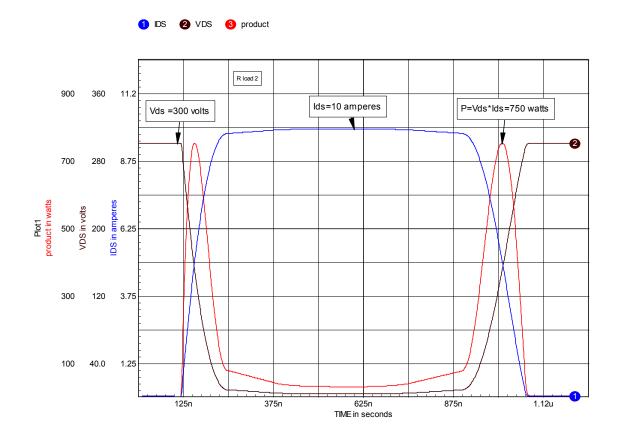

Figure 2-11, typical Vds and Ids switching waveforms with a resistive load.

Figure 2-11 shows the Vds and Ids waveforms associated with this circuit. During the off-state, Vds = Vin and Ids  $\square$  0. As Ids begins to rise at turn-on, the current in the resistor must also increase causing a proportional voltage drop across the resistor (IdsxR<sub>L</sub>) so that Vds = Vin -IdsR<sub>L</sub>. Vds begins to fall as the current waveform rises. When Ids = Vin/R<sub>L</sub>, Vds = 0 and the switch is in the on-state. Resistive load switching is considered to be low stress because the switch is not exposed to the maximum voltage and current simultaneously. This can be seen in figure 2-12 which is the load-line associated with figures 2-10 and 2-11. This is a typical example of a load-line diagram for a resistive load. In this example the traces for the on and off-transitions overlap so you see only a single straight line. The maximum instantaneous power occurs midway through the switch transition, which is 5 A x 150 V = 750 W.

Figure 2-12, Typical resistive load load-line.

The switching loss (P<sub>s</sub>) associated with resistive switching can be approximated from:

$$P_{s} = \frac{V_{g}^{2}}{6R_{L}}(t_{1} + t_{2}) = \frac{V_{g}I_{o}}{6}(t_{1} + t_{2})$$

$$I_{o} = \frac{V_{g}}{R_{L}}$$

(2-1)

Where  $f_s$  is the switching frequency.

# **Clamped inductive switching**

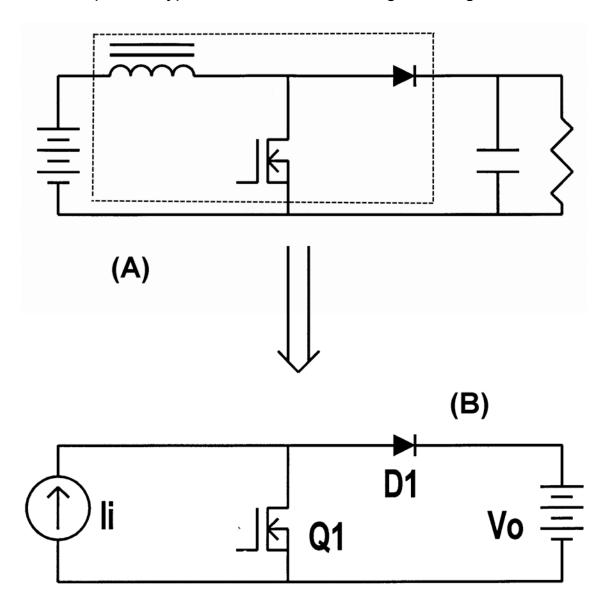

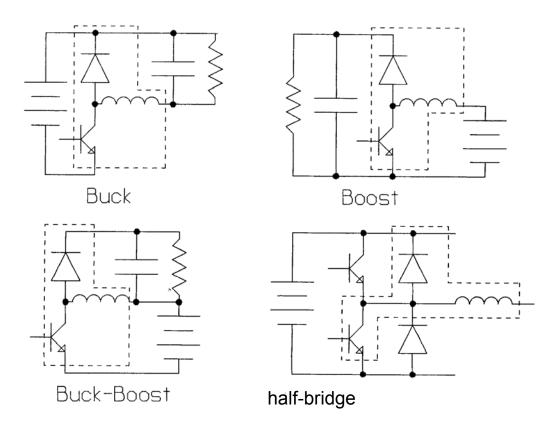

Resistive load switching has relatively low loss and peak switch stress. Unfortunately, that type of load is rare in power conversion. More often the load will be inductive. An example of a typical DC-DC converter is given in figure 2-13.

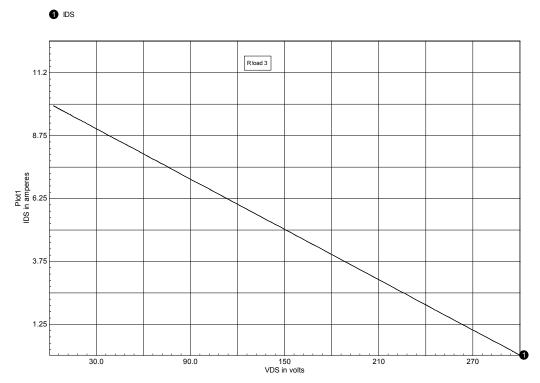

Figure 2-13, Boost DC-DC converter and its modeling approximation.

In the center of this converter (2-13A) there is an outlined network consisting of an inductor, a diode and a switch. This sub-network, and consequently this type of switching, is ubiquitous in power converters. To illustrate this point examples of other topologies where this sub-network appears are given in figure 2-14.

Figure 2-14, Switching topology examples.

For the purposes of this book we are concerned with the circuit behavior during switching transitions. Normally transition times will be very short compared to "on" and "off" time intervals so there is very little change in either the inductor current or the output voltage during transition intervals. To simplify modeling we can use this observation to replace the voltage source and input inductor with a constant current source and we can replace the output load and filter capacitor with a constant voltage source, as shown in figure 2-13B. For our purposes this simplification doesn't greatly change the waveforms we are concerned about and we will use this simplification extensively.

In the discussion which follows, and indeed throughout the remainder of this book, we will use the boost converter, operating in the continuous inductor current mode, as an example of "clamped inductive switching" as we discuss various snubber circuits. This type of switching is almost universal in power conversion so the discussion, even though limited to a specific converter topology, applies in general.

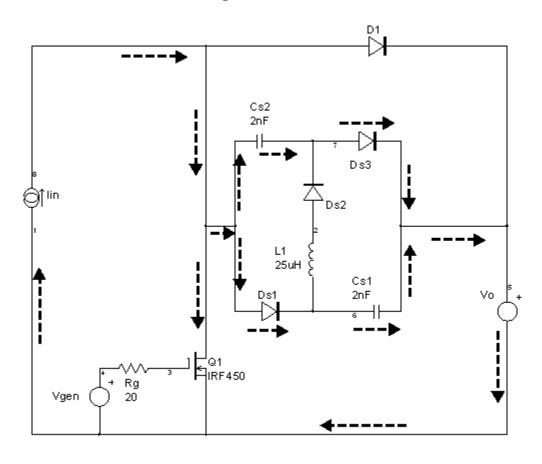

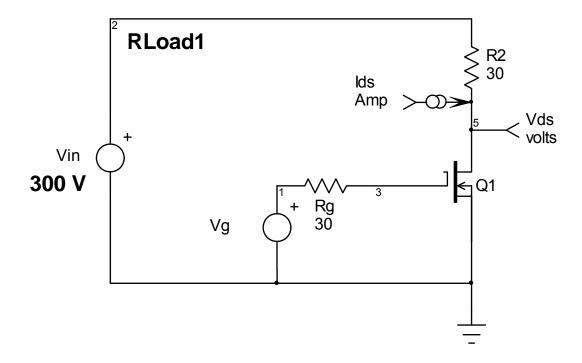

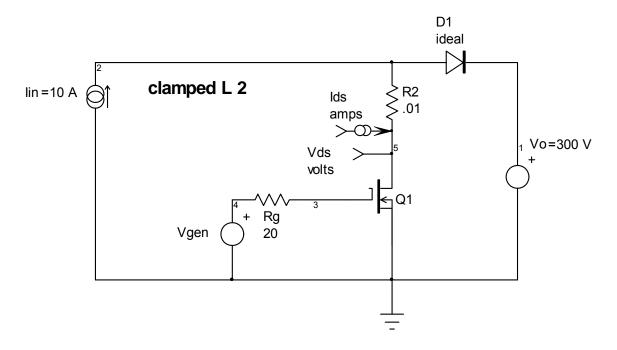

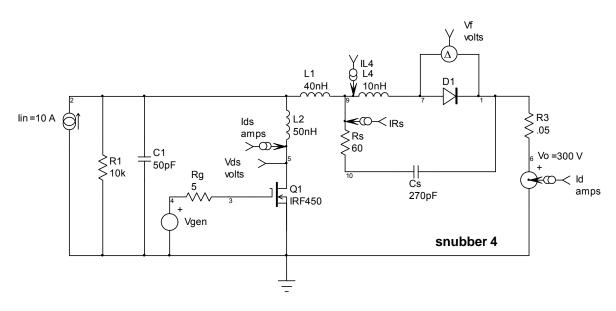

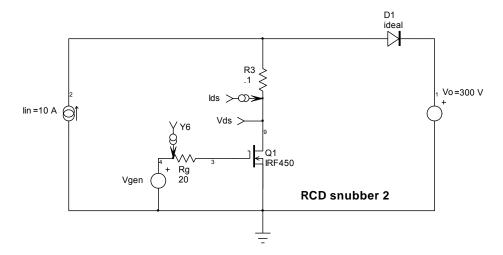

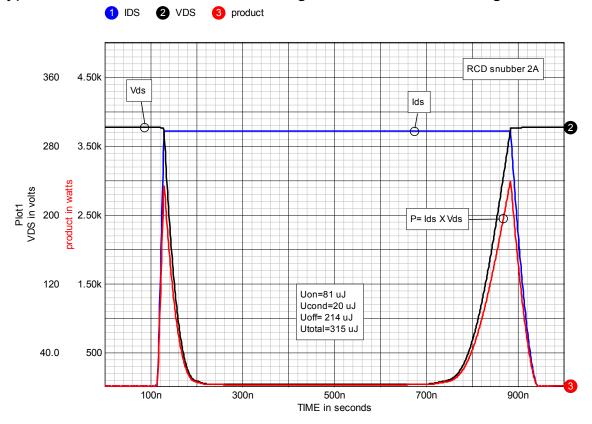

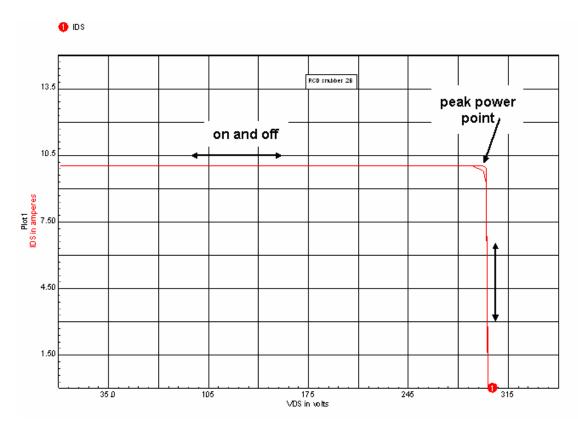

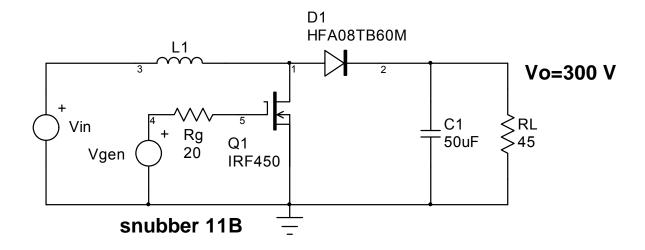

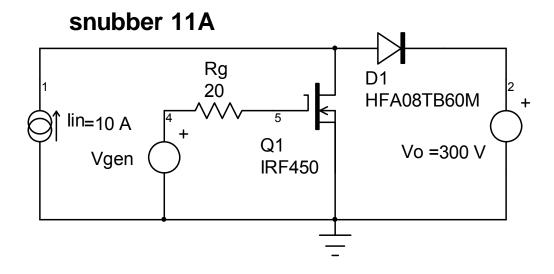

To model this type of load we can use the SPICE model shown in figure 2-15. Initially we'll use an ideal diode for D1 but later we will change to a real diode and see the effect on circuit operation. Resistor R2 is there as a means for metering lds and has little effect on circuit operation.

Figure 2-15, Clamped inductive switching circuit.

To make comparisons between switching scenarios easier, the nominal switch voltage has been set at 300 V and the switch current at 10 A as was done for the resistive switching example (figure 2-10). To provide continuity to the switching and snubber discussion to follow we will use these parameters consistently for most examples except where a change in value is needed to illustrate some point.

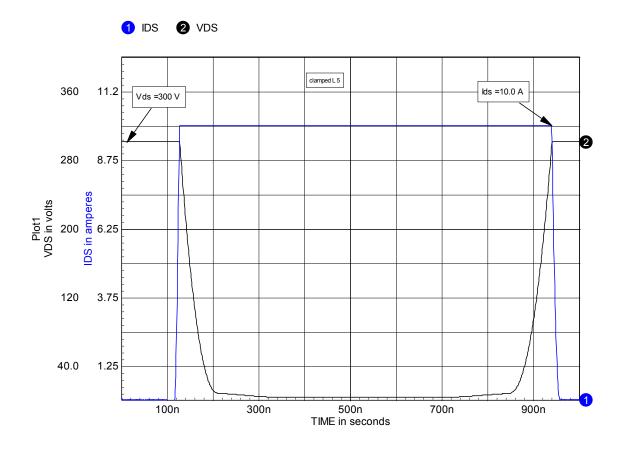

The waveforms associated with the circuit in figure 2-15 are shown in figure 2-16. Notice that at turn-on, Ids must rise to it's full value before Vds begins to fall. At turn-off Vds rises to it's full value before Ids can begin to fall. This means that the switch is exposed to both the maximum current and maximum voltage simultaneously. This is in contrast to the resistive switching case where Vds starts to fall as Ids begins to rise.

Figure 2-16, Idealized clamped inductive switching waveforms.

We can understand this behavior by examining the model. The connection point for lin,  $D_1$  and  $R_2$  forms a node at which Kirchhoff's current law must be satisfied: i.e. the sum of the currents into and out of the node must be zero at all times.

When  $Q_1$  is off, lin must flow through D1 into the output (Vo). This means that in the off-state Vds = Vo. As Q1 turns on and Ids begins to rise, the current in D1 will start to fall (being the difference between lin and Ids). However, as long as there is any forward current in D1, the diode will in effect be a short circuit and Vds = Vo. When Ids = Iin, the current in the diode is zero and it stops conducting. This allows Vds to fall. For the moment we will ignore the reverse recovery current inherent in real as apposed to ideal diodes.

As Q1 turns off, no current can flow in D1 until Vds reaches Vo, forward biasing D1, so lds (in Q1) remains constant. When Vds reaches Vo,  $D_1$  conducts and lds can begin to fall.

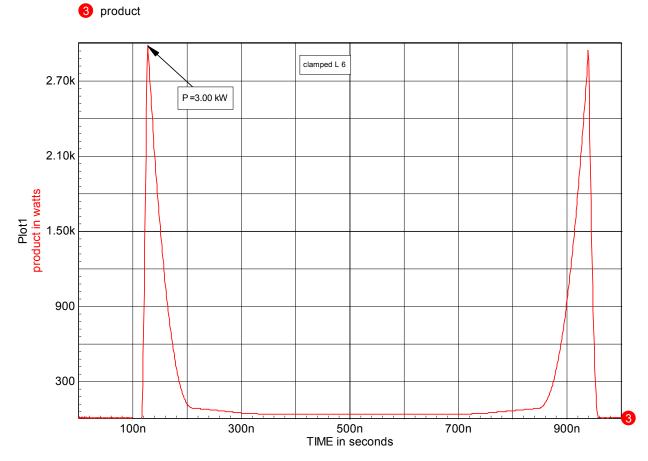

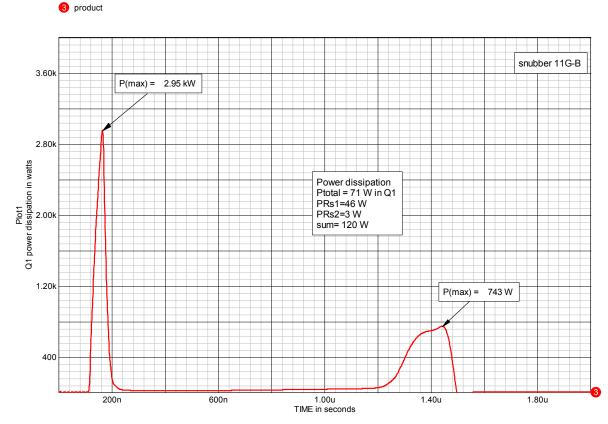

The instantaneous power dissipation in Q1 is shown in figure 2-17.

Figure 2-17, Power dissipation during the switching interval for the circuit in figure 2-15.

The peak power is now 3,000 W, which is four times the 750 W for the resistive switching example (figure 2-11) with the same switch peak voltage and current.

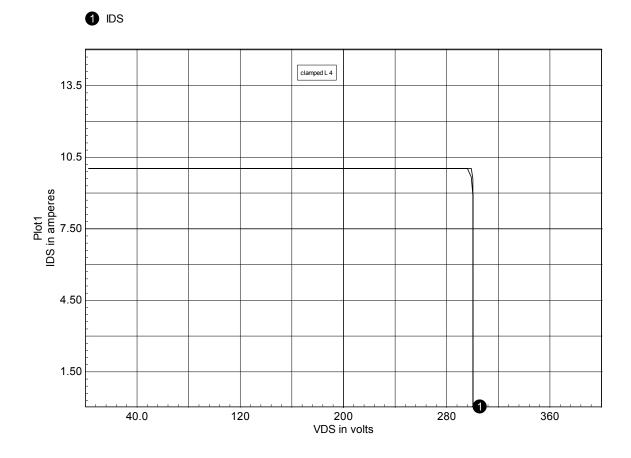

The load-line in figure 2-18 illustrates why the power is so high. This load-line is essentially rectangular with the maximum Vds and Ids occurring simultaneously on both turn-on and turn-off. The turn-on and turn-off traces overlap. This is often referred to as "hard switching" and is obviously much more stressful than resistive load switching.

Figure 2-18, Switching load-line for the circuit in figure 2-15.

The power loss due to switch transitions with a clamped inductive load can be approximated from:

$$P_{s} = \frac{V_{o} I_{in}}{2} (t_{1} + t_{2})$$

(2-2)

For the same values of maximum voltage and current, the loss for clamped inductive switching is three times that for resistive load switching and the peak power dissipation is four times. If we change D1 in figure 2-15 from an ideal diode to a real diode, which will display reverse recovery current, the situation gets even worse as shown in figure 2-19.

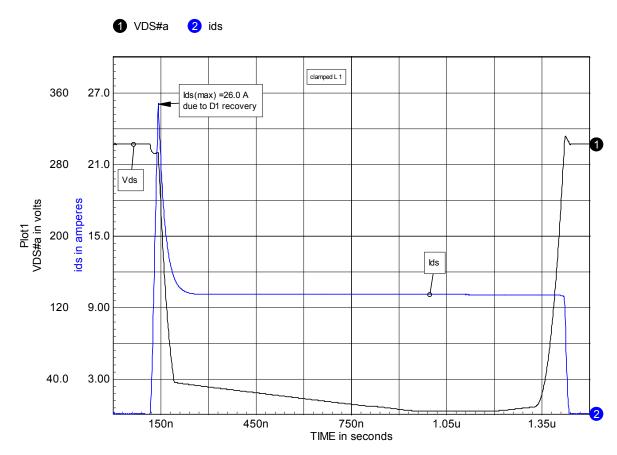

Figure 2-19, Switch waveforms with a real diode.

At turn-on there is a 26 A current spike due to the combination of input current and diode reverse recovery current. The peak power at turn-on is now about 7.8 kW. The use of a real diode leads to a drastically different load-line graph as shown in figure 2-20.

The turn-on current spike is large because of the rapid transition of the switch (high di/dt). If we slow down the switch, then this spike will decrease and the total switching loss may actually decrease. However, if we want to keep the switching time small then we will have to use some form of snubber to limit the diode reverse recovery di/dt.

Figure 2-20, Clamped inductive switching load line with a real diode.

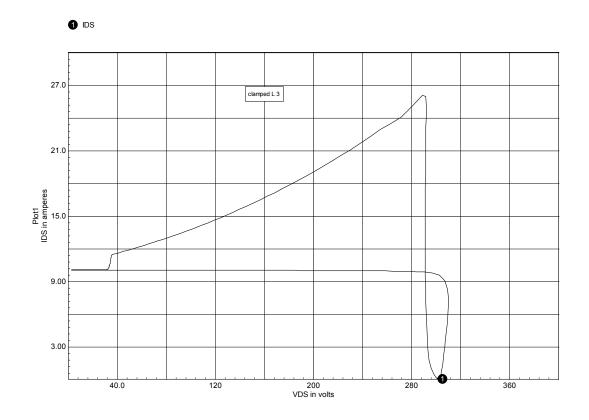

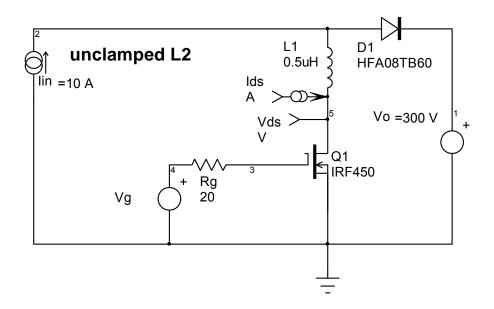

# **Unclamped inductive switching**

Figure 2-21, switch with unclamped inductance.

Any practical circuit will have some inductance in series with the switch. This can be due to both layout parasitic inductance and semiconductor package inductance. We can use the model in figure 2-21 to explore the consequences of adding this parasitic inductance.

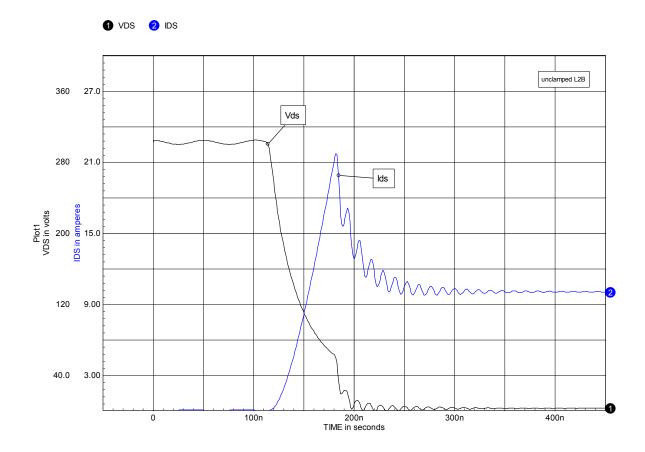

A 500 nH parasitic inductance (L1) has been added in the switch drain. From this model we get the waveforms shown in figure 2-22.

Figure 2-22, Vds and Ids waveforms with unclamped drain inductance.

Obviously the waveforms have changed. In some ways for the better but in others for the worse. Let's start by expanding the time scale during turn-on (figure 2-23) to take a closer look at this interval.

Figure 2-23, Ids and Vds at turn-on, expanded time scale.

Notice that Vds now begins to fall <u>before</u> Ids has reached it's maximum. The effect of L1 is to reduce the turn-on stress. The decrease in Vds is due to a voltage drop across L1 as Ids rises [V=L x d(Ids)/dt]. This is the basic principle of the turn-on inductive snubber. In this example L1 is also large enough to reduce the diode reverse recovery current spike, which is another feature of an inductive turn-on snubber.

While L1 helps at turn-on, at turn-off, a large ringing voltage spike is now present at turn-off. The ringing comes from the combination of the L1 and the output capacitance of the switch. If we want the benefits of L1 at turn-on we will have to add some network to the circuit to suppress the turn-off voltage spike. This will be dealt with in chapter 2.

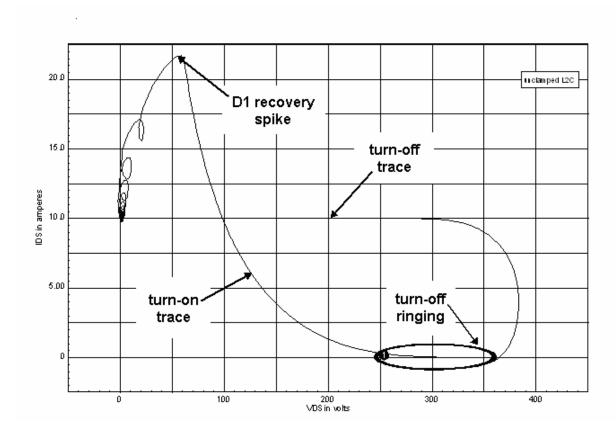

The load-line graph associated with these waveforms is shown in figure 2-24.

Figure 2-24, load-line graph with unclamped drain inductance.

During turn-on this load-line has greatly reduced stress, including a reduced diode recovery current spike. However, at turn-off we have a voltage spike and severe ringing. There is also ringing at turn-on after the point where D1 reverse recovery current has peaked and is falling. This is the point where D1 can support reverse voltage.

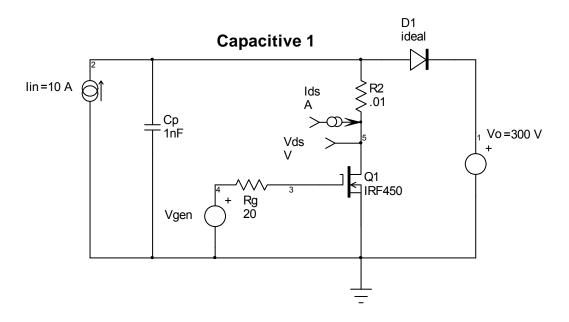

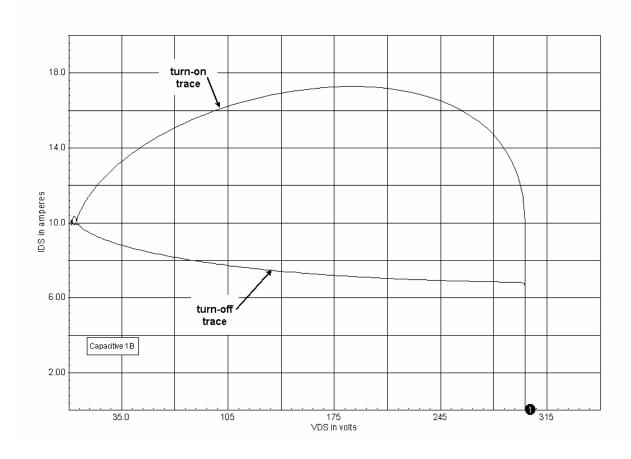

## **Capacitive switching**

Capacitance is another common parasitic element. There will be the junction capacitance of the switches and diodes plus stray capacitance from the circuit layout, semiconductor package mounting, etc. We can examine the effect of shunt capacitance by adding C1 to figure 2-15, keeping the ideal diode, as shown in figure 2-25.

Figure 2-25, adding parasitic capacitance to the circuit.

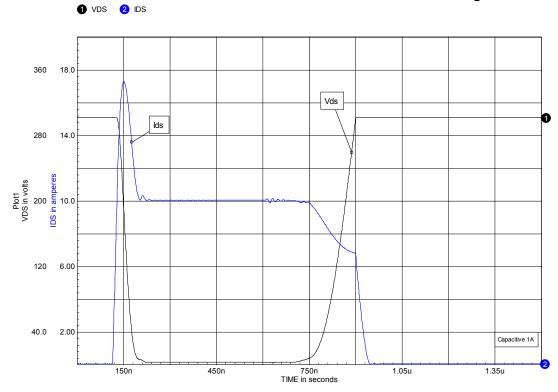

The waveforms associated with this model are shown in figure 2-26.

Figure 2-26, waveforms for capacitive load switching.

At turn-on there is a current spike due to the discharge of C1. Since the diode is ideal in this example, there is no reverse recovery current spike. In a circuit using a real diode then both current spikes would add together. The presence of parasitic capacitance creates additional stress at turn-on but it significantly reduces the stress at turn-off. Because the capacitance provides another path for current flow as the switch turns off, the switch current can now begin to fall immediately as  $V_{\rm ds}$  begins to rise. For a sufficiently large value of capacitance, the turn-off stress can be reduced to near zero. Unfortunately this is achieved at the cost of higher turn-on stress and the loss of the energy stored in the capacitor. The effect of shunt capacitance is the basis for turn-off snubbers. In the case of a snubber however, some arrangement has to be made to control the turn-on current spike.

The load-line for this kind of switching is shown in figure 2-27.

Figure 2-27, Load-line for capacitive load switching

#### **Switching with real loads**

In addition to the desired components, any practical circuit will have parasitic elements due the non-ideal character of desired components and the physical layout. Parasitics are generally unintentional but some are unavoidable. The use of good layout practices is a vital part of reducing parasitic elements.

The best practice is to minimize the parasitic inductances and capacitances due to the physical layout before employing snubbers. Clean up the circuit first, then add a snubber.

The use of a snubber to remedy the effects of poor layout is a very bad practice.

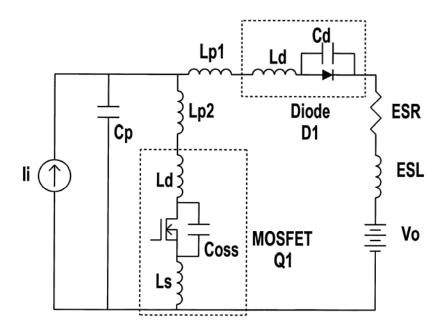

Figure 2-28 extends the idealized circuit introduced in figure 2-15 to include typical parasitic elements.

Figure 2-28, Typical parasitic elements in a converter circuit.

Let's take a moment and look at each of the parasitic elements:

Cp represents the shunt capacitance of the input inductor and also stray capacitance of the interconnecting conductors between the input inductor,Q1 and D1.

- Lp2 is the wiring inductance associated with Q1.

- In Q1, Ld and Ls are the lead and bonding wire inductances within the device package. Coss is the output capacitance and may also include capacitance from a heat sink.

- Lp1 is the wiring inductance associated with the diode.

- In D1,Cd is the capacitance associated with the diode junction and Ld is the internal package inductance.

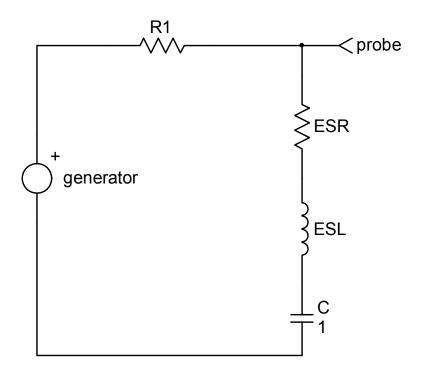

- The output filter capacitor will have both ESR (equivalent series resistance) and ESL (equivalent series inductance).

- In addition there will be stray capacitance associated with device heat sinks and transformer windings.

- Transformers usually introduce leakage inductance, which can be substantial.

Figure 2-28 is just a simple example. More complex circuits will have even more parasitic elements and these parasitics will play an active role in circuit behavior.

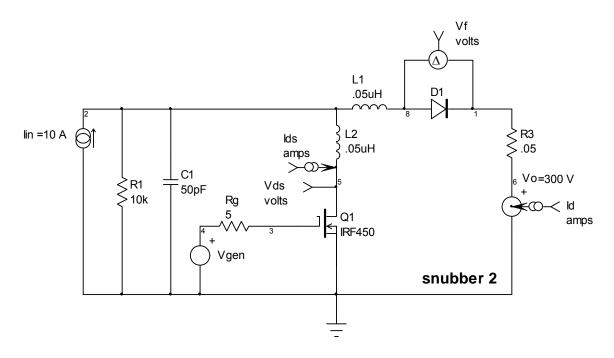

# Effect of parasitics on circuit waveforms

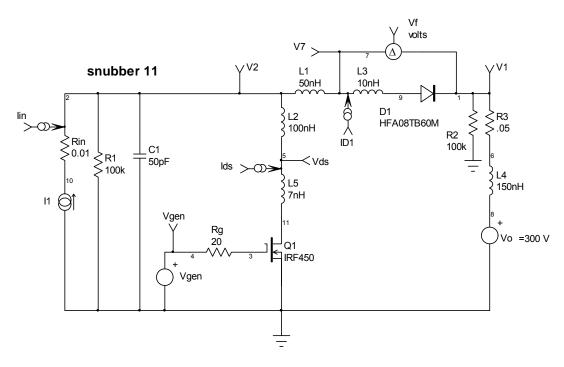

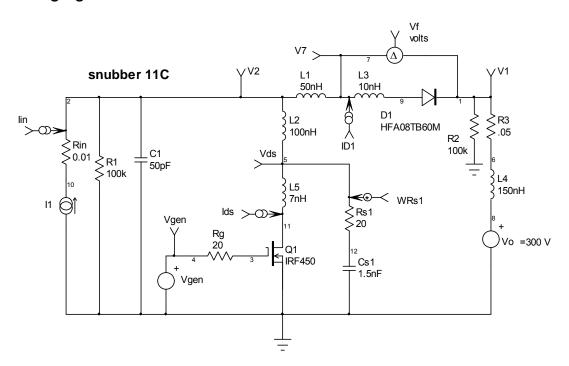

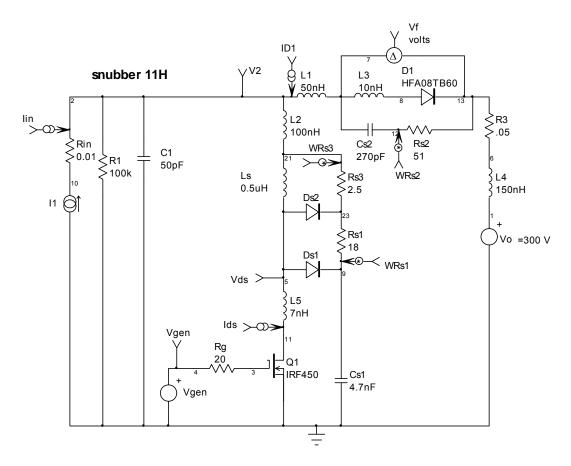

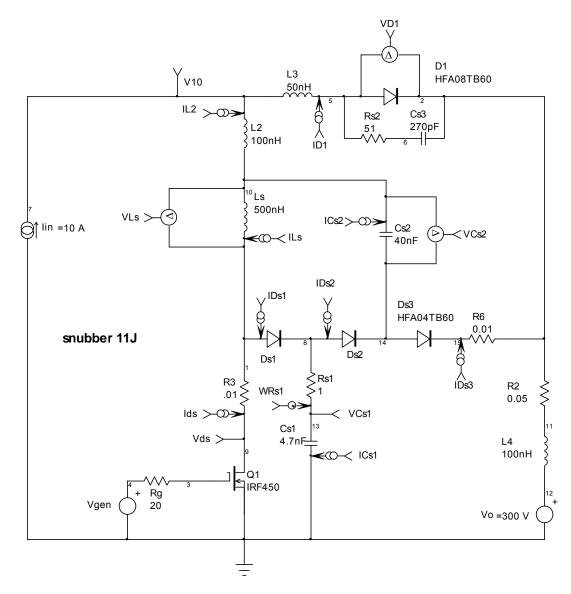

To investigate their effect, we can add parasitic elements to a SPICE model as shown in figure 2-29. Note, D1 is now a real diode (an IR, HFA08TB60). Parasitic junction capacitances are not shown in figure 2-29 but are built into the device sub-circuits. Device models may also contain typical lead inductances internal to the package. The values chosen for the parasitics are reasonable approximations for a circuit of this power level but you should keep in mind that the values can be much larger in some circumstances. Particularly when transformers with leakage inductance are employed.

Figure 2-29, SPICE model with parasitic elements added.

A number of metering (V and I) points have been included in the model. This clutters up the schematic a bit but is very handy for deciphering circuit behavior. When modeling complex circuits extensive metering is often used.

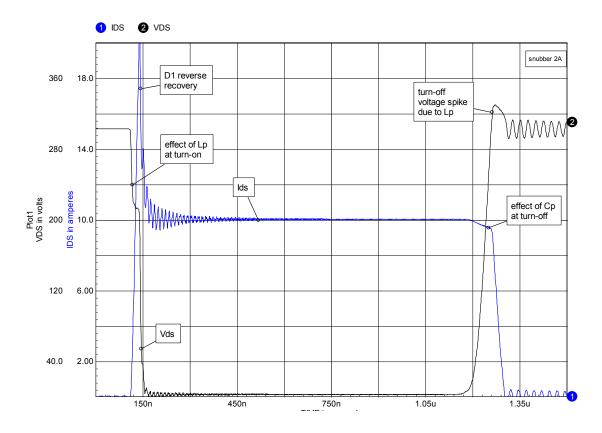

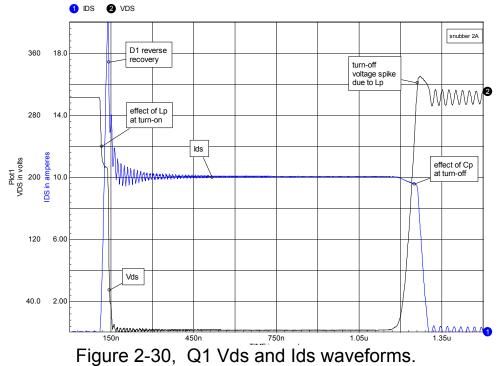

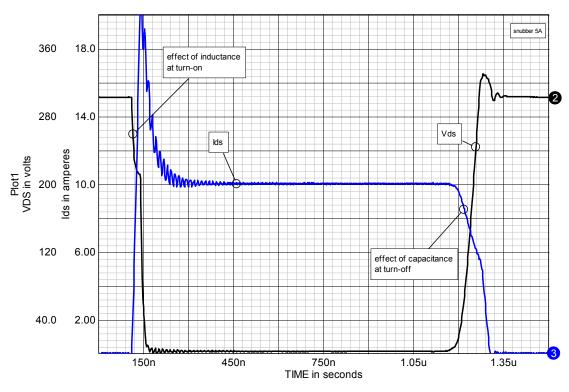

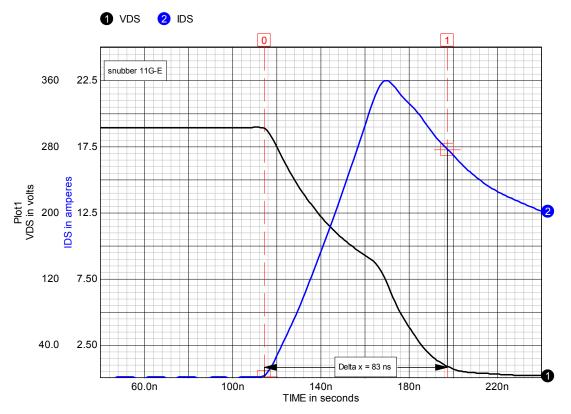

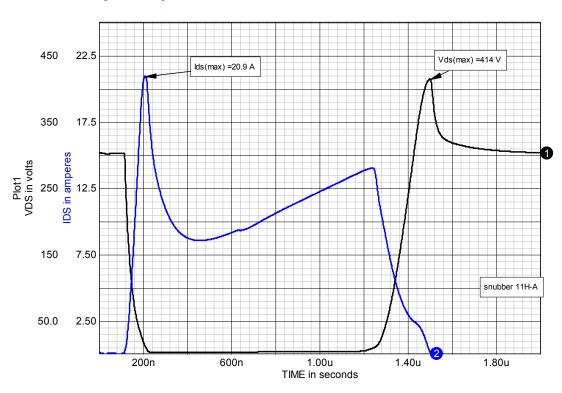

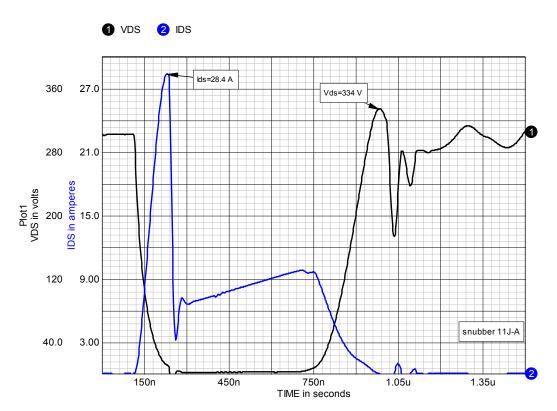

Running the simulation, we get the waveforms shown in figure 2-30. The first thing we notice is the ringing in the turn-on current and turn-off voltage waveforms by the combination of the parasitic inductances (Lp) and capacitances (Cp). Looking a bit closer we can see the initial dip in Vds at turn-on and the Vds voltage spike at turn-off, are both caused by Lp. At turn-on the diode reverse recovery spike on lds is present and at turn-off we can see the effect of Cp on Ids.

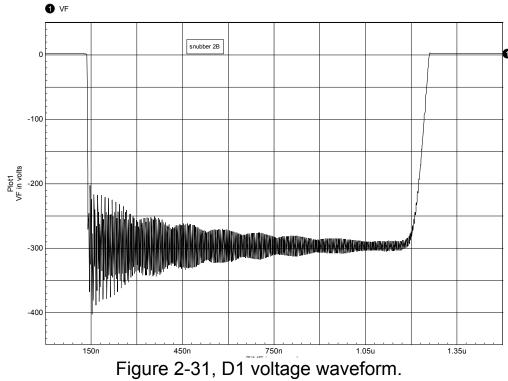

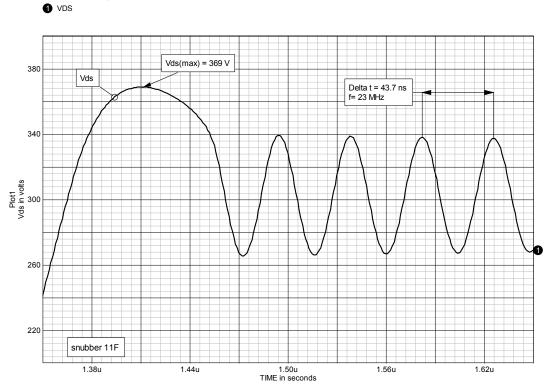

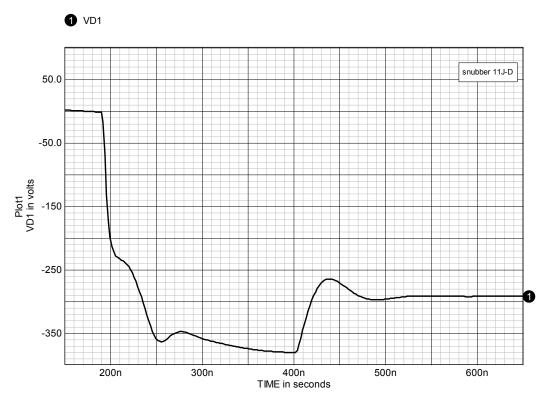

The Q1 waveforms don't look all that bad but when we look at the voltage waveform across D1 shown in figure 2-31, things don't look good at all.

Figure 2-30, Q1 Vds and Ids waveforms.

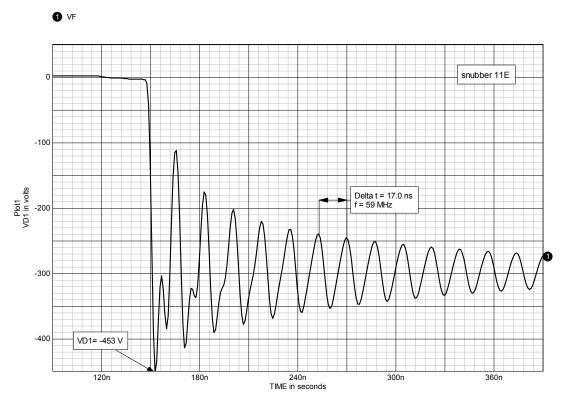

Figure 2-31, D1 voltage waveform.

The amplitude of the voltage ringing is large and has simultaneous ringing at two frequencies. This is not too surprising since the overall circuit has multiple inductances and capacitances: i.e. it is a multipole network. In an ideal circuit the diode reverse voltage would be 300 V but the overshoot here is about 100 V above that. This waveform needs be damped to reduce diode stress and EMI.

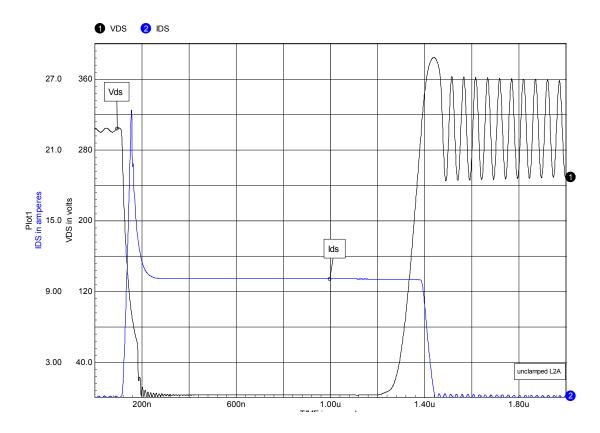

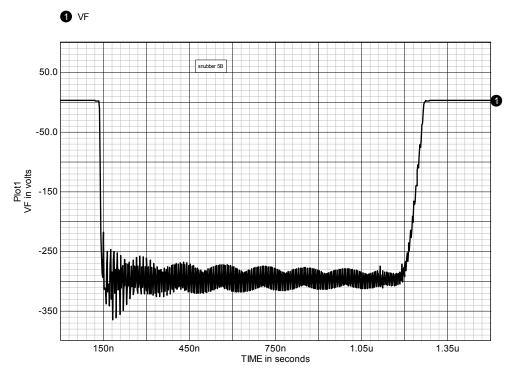

What would happen if L2 were even larger, say 500 nH? This would be possible in a circuit with transformer leakage inductance in series with the switch or even excessively long leads to Q1 and D1.

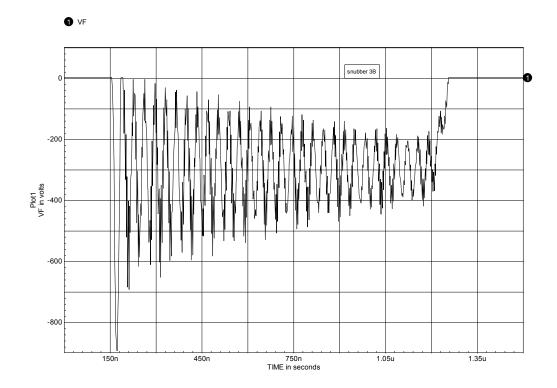

Figures 2-32 and 2-33 show the impact of increasing L2 from 50 to 500 nH. The voltage and current ringing are now very large and continue during the entire switching cycle. D1 reverse voltage risen to almost 1 kV and there is a 120 V turn-off spike on Vds. Clearly parasitic inductance is something we want to minimize!

Figure 2-32, Q1 Vds and Ids waveforms with L2=500 nH.

Figure 2-33, D1 voltage waveform with L2=500 nH.

## <u>Unintentional overlapping conduction in switches</u>

A very common problem in circuits containing more than one switch is simultaneous conduction of two or more switches at a time when this is not desired. Switches have four operating states: on, off, transition from off-to-on and transition from on-to-off. Generally the problem falls into one of two categories. The first case is where some other switch in the circuit is triggered on inadvertently while one switch is in full conduction. This is frequently a problem in thyristor circuits due to undesired dV/dt induced turn-on and it can lead to catastrophic failure of the switches. The second and more common case is where a second switch begins to turn-on while a first switch is still in transition from on-to-off. How serious this is depends on where in the individual turn-on/turn-off transitions the two switches are. The consequences can range from a modest increase in loss to device destruction. Usually we try to design the circuit so that these two cases cannot occur in any normal operating mode but we are not always successful. Snubber circuits can be used to mitigate the effects of these kinds of events.

A very common example of overlapping conduction is the reverse recovery current spike through a diode. The diode is a switch which may very well be conducting when another switch is turned on. The result as we have already seen, can be a large current spike in both switches.

The same problem can occur when two active switches are used. This can be illustrated using the model in figure 2-34.

Figure 2-34, idealized half-bridge converter circuit.

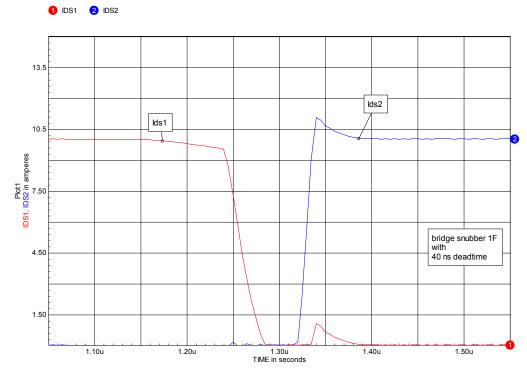

In this circuit Q1 and Q2 conduct alternately. A dead-time is usually built into the drive waveforms to assure that both switches are not on simultaneously. Typical Ids waveforms for Q1 and Q2 are shown in figure 2-35, where the dead-time is very evident.

Figure 2-35, normal Ids waveforms for Q1 and Q2.

Figure 2-36, an example of Ids1 and Ids2 waveforms during conduction overlap.

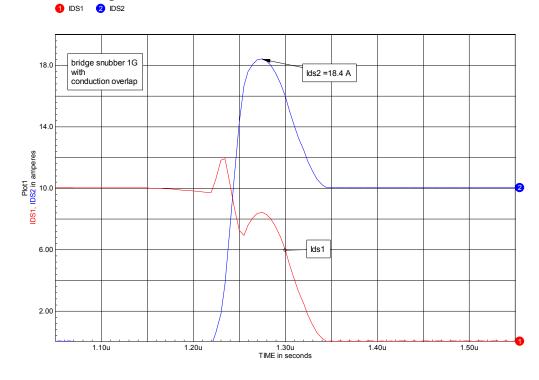

Suppose however, that the dead-time is not sufficient and there is conduction overlap. An example of this is given in figure 2-36.

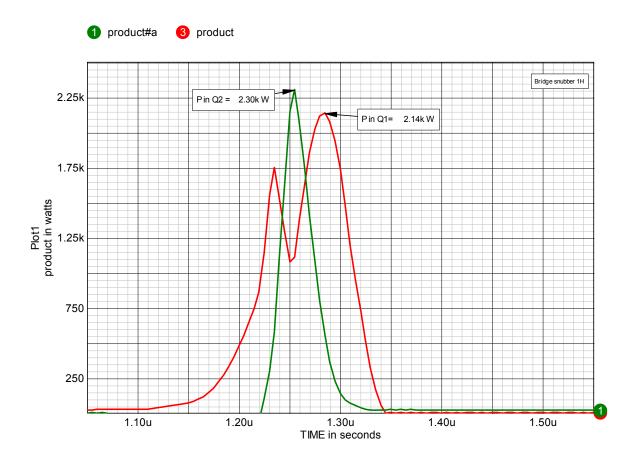

When overlapping conduction is present, the power dissipation in each switch may be quite high, as shown in figure 2-37.

Figure 2-37, power dissipation in Q1 and Q2 during Q1 turn-off.

While this kind of overlapping conduction is usually attacked by providing ample dead-time, due to component variations that is not always successful. One reason is the need to maximize the switch duty cycle to improve overall circuit efficiency. This can lead to making the dead-time too short for worst case component and temperature variations. While the first line of defense is adequate dead-time, an inductive turn-on snubber can provide additional protection.

#### Lack of desired overlapping conduction

The converter circuits in which we typically worry about overlapping conduction are for the most part derived from the buck topology. However, there is another entire class of converter topologies<sup>[387]</sup> which are derived from the boost topology. Multi-switch versions of these circuits usually require that at least two switches be in simultaneous or overlapping conduction. The problem which arises when the switch conduction fails to overlap is the dual<sup>[387]</sup> to the overlapping conduction problem in buck derived converters. You get a voltage spike during switch transitions rather than a current spike. This problem is just as undesirable as the current spike and is usually controlled by careful attention to the switch drive waveforms. For abnormal operating conditions and from reliability considerations, some form of snubber or voltage clamp is usually employed to protect the switches in these topologies.

# **Chapter 3**

# **RC**-snubbers

An RC-snubber, or damping network as it is sometimes called, consisting of a series R and C is by far the most commonly used snubber. One would think that designing such a snubber would be easy but to do it analytically turns out to be not so simple. The problem is that the snubber is usually imbedded in a complex multi-element network with several inductances and capacitances, most of them parasitic, some varying with voltage. This makes closed analytic solutions intractable for the purposes of day-to-day design work. In addition, it is necessary to use some judgment in choosing what peak voltages and/or currents are acceptable and also acceptable losses.

The approach adopted here is a combination of simple analytic models, approximations which lead to a good "first guess" and some final adjustment in the actual circuit. This is not a very elegant method but it usually converges quickly to an acceptable solution. Those interested in a more analytic approach, are referred to the classic paper by McMurray<sup>[287]</sup> and in this section we will use some of the results of Dr. McMurray's paper. The McMurray paper is a good example of the analysis complexity for even simple cases.

## **Examples of RC-snubber use**

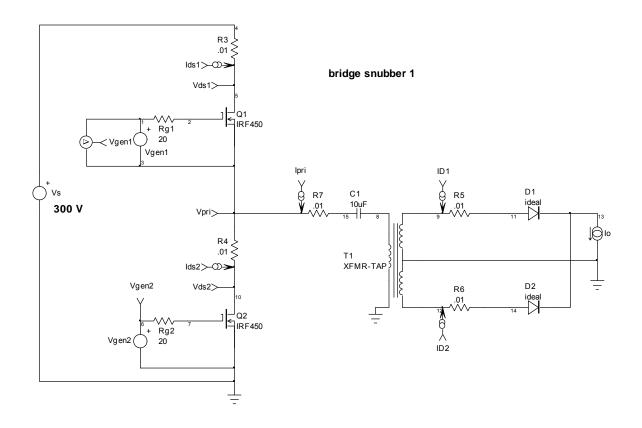

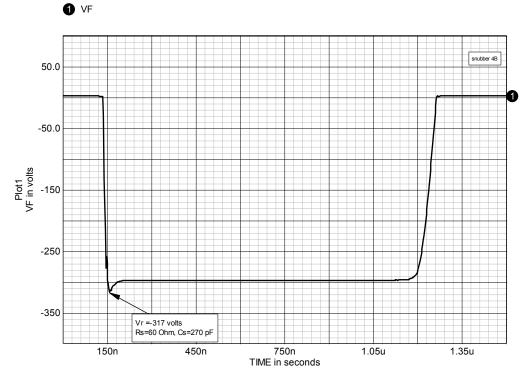

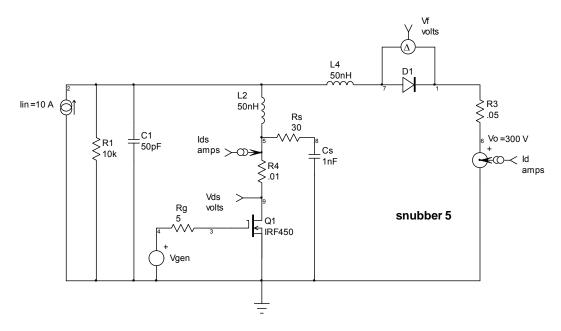

To illustrate the use of an RC-snubber we'll take a look at damping the ringing voltage waveform across D1 which was shown in chapter 2 (figure 2-31). We will modify the model in figure 2-29 by adding an RC-snubber (Rs & Cs) across D1 as shown in figure 3-1. For the moment we will use some typical values for Rs and Cs without explanation because I just want to demonstrate the general behavior of an RC snubber. A bit later we'll see how the values for Rs and Cs are determined in a particular application.

Figure 3-1. RC-snubber across D1.

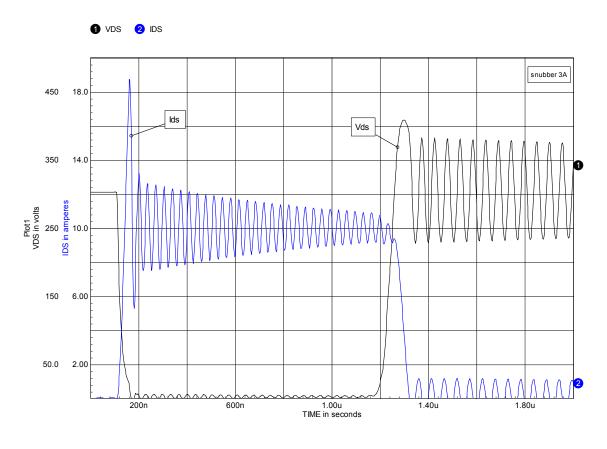

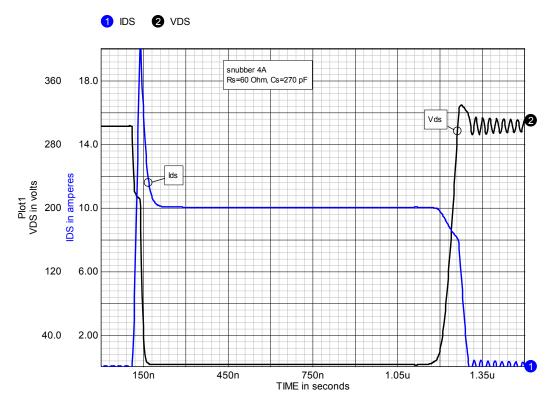

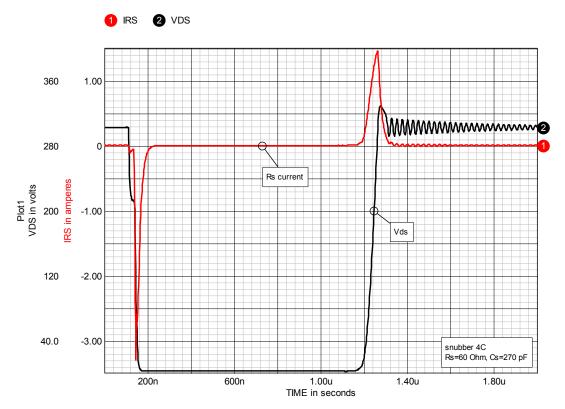

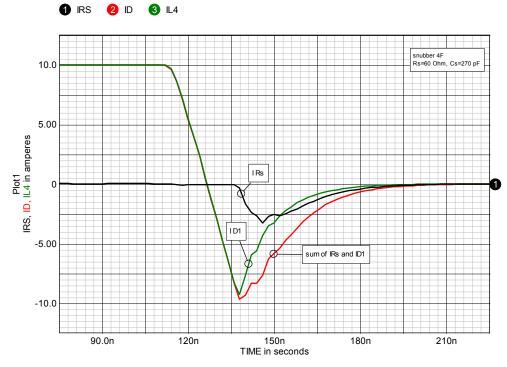

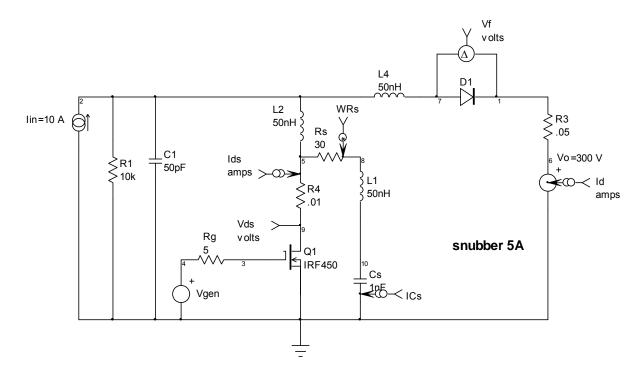

Note that L1, in figure 2-29, has been divided into L1 and L4 in figure 3-1 to simulate the effect of package inductance: i.e. the snubber is across the outside of the package and not directly across the diode junction. The associated Vds and Ids waveforms are shown in figures 3-2 and 3-3.

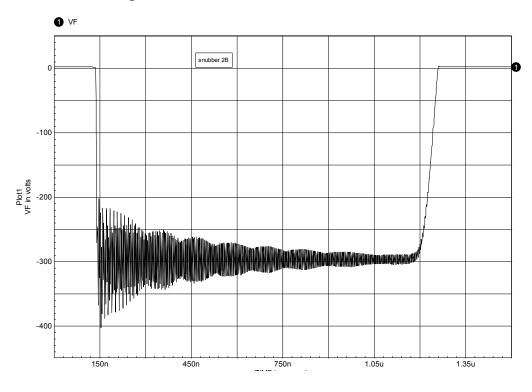

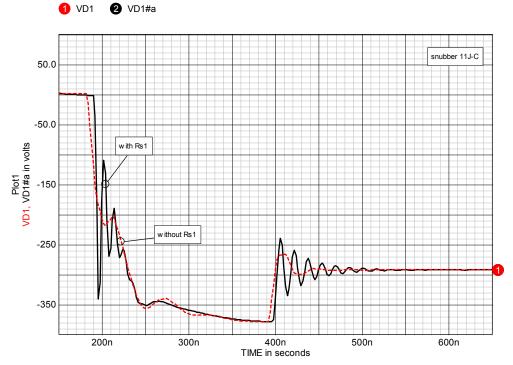

Comparing figures 2-31 and 3-2 (figure 2-31 is repeated here for convenience), it is clear that the voltage waveform across D1 has been dramatically improved. This is a very good example of just how useful simple snubbers can be and why they're so popular.

Comparing figures 2-30 and 3-3, the improvement is not so dramatic. The Q1 turn-on current and voltage ringing are gone but the effect at turn-off is hardly detectable. But there is an important difference in the Ids current spike at Q1 turn-on, it is somewhat wider. This is addition current in Q1 at turn-on is due to the charging of Cs, through Rs and Q1, at Q1 turn-on. This increase in turn-on current is one of the undesired "side-effects" which appear when a snubber is added to the circuit.

Figure 3-2, D1 voltage waveform with snubber across D1.

Figure 3-3, Q1 lds and Vds waveforms with a snubber across D1.

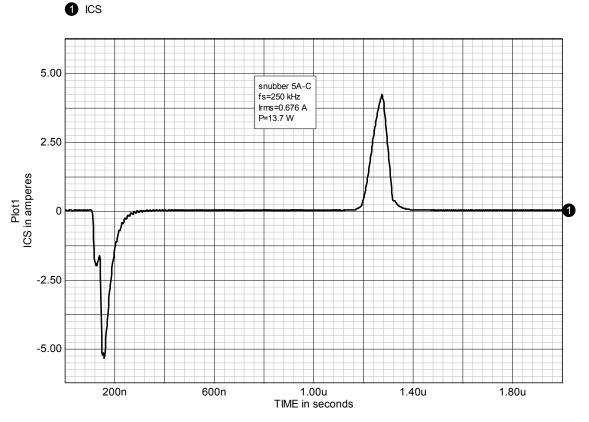

In steady state, when Q1 is off and D1 is conducting, Cs will be discharged essentially to zero. While Q1 is on, Cs is charged to Vo=300 V through Q1 and when Q1 turns off and D1 turns on, Cs is discharged back to zero through D1. Figure 3-4 shows the current waveform in Rs and Cs as Q1 turns on and off.

The current in Cs consists of short, high amplitude pulses, with a substantial RMS value, which can stress the snubber capacitor. Pulsed current waveforms with high peak and RMS values are typical of many snubber circuits. This is why snubber capacitors must be carefully chosen. Choices for snubber capacitors are discussed in chapter 6.

The current pulse associated with Q1 turn-on flows in Q1 and <u>adds</u> to the D1 reverse recovery current spike. This can be seen more clearly in figure 3-5 which gives the current waveforms in L4 and Rs and their sum, which is the current spike in Q1 at turn-on.

Figure 3-4, snubber current waveform.

Figure 3-5, components of Q1 lds turn-on current spike.

The wider turn-on current spike in Q1 is due to the addition of the Cs charge current to the D1 reverse recovery current.

The peak amplitude of Ids is directly related to the value for Rs, the larger we make Rs the smaller the spike will be. But, as we will see shortly, there will be an optimum value for Rs which gives the most effective damping and/or the smallest peak voltage. Sometimes we may have to select a compromise value for Rs which trades lower peak current for somewhat higher peak voltage.

The important lesson here is that while the snubber suppresses the ringing across D1, and reduces some ringing elsewhere in the circuit, it introduces additional current stress on Q1. The introduction of new current or voltage stresses is a typical consequence of adding a snubber to a circuit. This has to be taken into account when designing snubbers. There is no free lunch! It is possible however, to design snubbers with auxiliary switches which add little or stress to the power switches<sup>[27,45,116,123,150,157,185,190,254,278,438]</sup>.

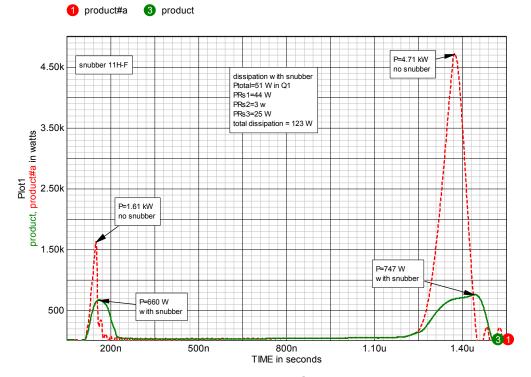

Another effect of adding a snubber, is the power dissipation in Rs. When Cs is discharged through D1 essentially all the energy ( $U_1$ ) stored in Cs will be dissipated in Rs. When Q1 turns on and Cs is recharged, energy will again be dissipated in Rs. As a result, the energy loss per switching cycle will be:

$$2U_1 = CsV^2$$

(3-1)

The power dissipation in Rs  $(P_{Rs})$  will depend on the switching frequency  $(f_s)$ :

$$P_{Rs} = CsV^2f_s \qquad (3-2)$$

Adding the snubber introduces loss. It may be that some other losses will be reduced but this loss is still a matter of concern. The larger we make Cs the greater will be the beneficial effect of the snubber but also the greater will be the loss introduced by the snubber. Typically we try to choose a value for Cs which is the minimum that gets the job done, although as shown in chapter 7 (see figure 7-11 and associated text), sometimes it is desirable to reduce the switch loss at the price of increased loss in Rs.

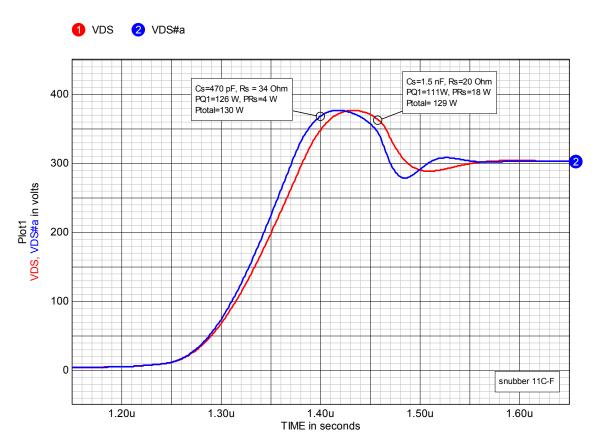

As we've just seen, adding an RC-snubber across D1 only partially reduces the ringing waveforms associated with Q1. Let's shift the snubber from D1 to Q1 as shown in figure 3-6 and examine the effect on the circuit waveforms. In this example we have made Cs larger (1 nF) and reduced Rs to 30 Ohm.

Figure 3-6, RC-snubber across Q1.

The waveforms associated with Q1 are shown in figure 3-7. Comparing the waveforms in figures 2-30 (repeated here for convenience) and 3-7, we see that the primary effect of placing the snubber across Q1 is to damp the voltage ringing at turn-off but there is not much effect on the turn-on current ringing. Note also that at Q1 turn-off lds now begins to fall before Vds reaches Vo. This reduces Q1 loss.

The voltage waveform across D1 is shown in figure 3-8. Comparing figures 2-31 and 3-8, we see that the D1 voltage ringing is reduced with the snubber across Q1 but not by nearly as much as when the snubber was across D1. Typically there are multiple inductances and capacitances in the circuit and you will very likely have to use more than one RC-snubber. Because there will be some interaction between snubbers, you may have to juggle the component values to get the desired effect with minimum power loss.

2 VDS 3 IDS#a

Figure 3-7, Q1 waveforms.

Figure 3-8, voltage waveform across D1.

We've just seen an overview of how the RC-snubber works and how it might be applied in a given circuit. Now we need to look in much greater detail to see how to design such a snubber for a given application.

#### A closer look at RC-snubber behavior

An RC-snubber is usually used to limit the peak voltage ( $V_p$ ) across a device and/or to damp an oscillatory waveform. In most cases limiting  $V_p$  will result in adequate damping so in the following discussion we will make limiting  $V_p$  our primary goal but keep an eye on waveform damping as we go along.

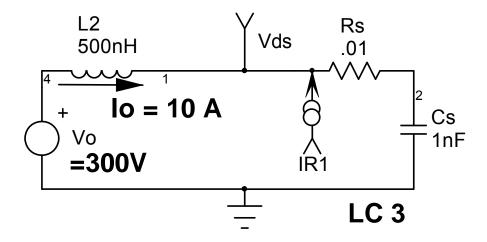

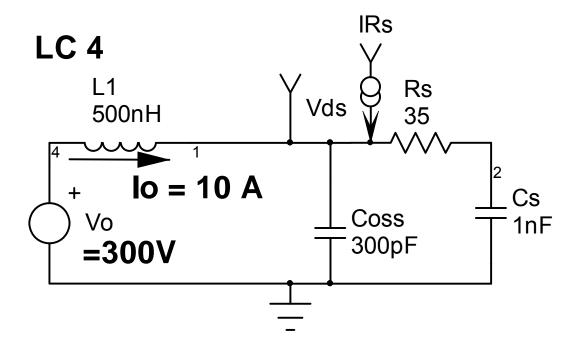

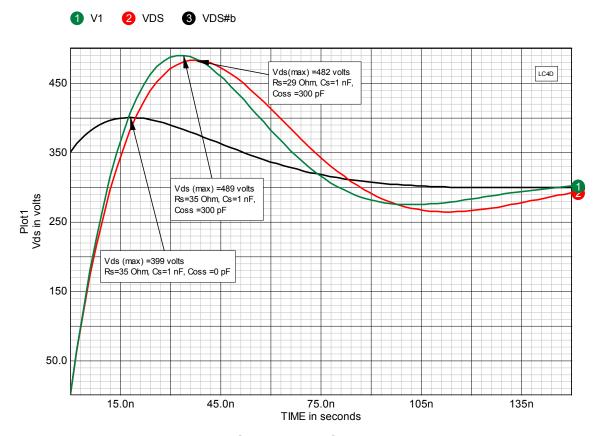

The discussion will begin with simple, idealized models which illustrate circuit behavior. Then components will be added making the model more realistic to show the effect of additional parasitic elements and the finite switching times of real devices. We'll end up with the circuit in figure 3-6 except that L2=500 nH, a reasonable value if there is some transformer leakage inductance present.

We will start with the simple R-L-C circuit shown in figure 3-9. The network represents the circuit state (of figure 3-6) just after the Q1 has turned off, with L2 representing parasitic drain inductance, Vo represents the output voltage to which the end of L2 (at node 4) is clamped through D1, lo is the current in L2 at t=0 and Rs-Cs represent the snubber. What we're interested in is the waveform for Vds as we vary Rs and Cs.

Figure 3-9 Equivalent circuit just after Q1 turn-off

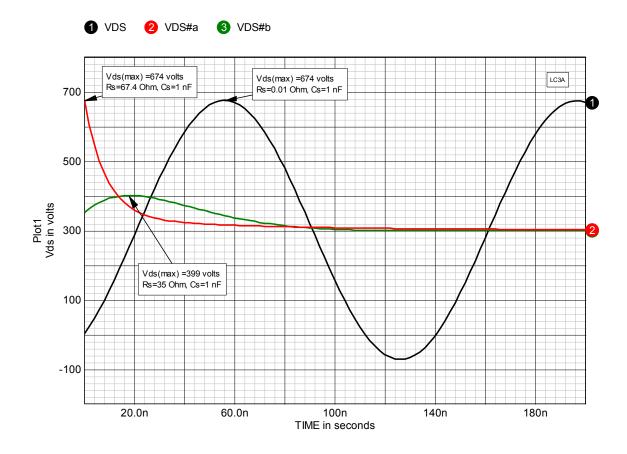

If Rs=0, then we can predict the peak value for Vds from<sup>[287]</sup> from the following expression:

$$\frac{V_{ds}}{V_o} = 1 + \sqrt{1 + \left(\frac{I_o}{V_o}\right)^2 \left(\frac{L2}{Cs}\right)} = 1 + \sqrt{1 + \left(\frac{I_o}{V_o}\right)^2 Z_o^2}$$

(3-3)

For the values given in figure 3-9,  $V_p$  = 674 V (from equation 3-3).

That's for Rs very small. What if we let Rs=67.4 Ohms? The waveforms for these two values of Rs are shown in figure 3-10.

Figure 3-10, Vds waveform for different values of Rs.

For Rs=0,  $V_p$ =674 V as predicted from equation (3-3) and the waveform is undamped. On the other hand, for Rs=67.4 Ohm,  $V_p$  =Io\*64.7 = 674 V, which is no improvement in  $V_p$  but the waveform is now very well damped. If we make Rs larger,  $V_p$  will only increase which is not what's wanted. We want to decrease  $V_p$ . Suppose we make Rs=35 Ohm. The effect of this on  $V_p$  is shown by the third waveform in figure 3-10. Now  $V_p$ =399 V which is a reduction of 275 V.

The point of this exercise is to show that there will be some optimum value for Rs, between zero and 67 Ohms, which gives the minimum value for  $V_p$ . Given that the maximum voltage rating for an IRF450 is 500 V and normal practice would be to derate by 20% (to 400 V),  $V_p$ =399 V is a safe value. If we adjust the value of Rs a bit we will find that the Vds minimum is quite broad and 35 Ohm is pretty close to the best choice we can make for that particular value of Cs. If we want to reduce  $V_p$  further we'll have to use a larger value for Cs.

We'll examine the choice of Cs shortly but first we need to generalize how we find the optimum Rs for a given choice of Cs and parasitic values.

#### Finding the optimum value for Rs

Besides cut-and-try in SPICE, how do we find the optimum value for Rs? At the very least we need a way to make a good initial guess.

The ringing frequency (f<sub>o</sub>) for the network in figure 3-9 is:

$$\omega_o = 2\pi f_o = \frac{1}{\sqrt{L2Cs}}$$

(3-4)

The characteristic impedance  $(Z_0)$  of the network is defined by:

$$Z_o = \sqrt{\frac{L2}{Cs}}$$

(3-5)

For the values of  $Vp/V_0$  normally acceptable ( $Vp/V_0<2$ ), the optimum value for Rs will be in the following range:

$$Z_o \leq Rs \leq 2Z_o$$

(3-6)

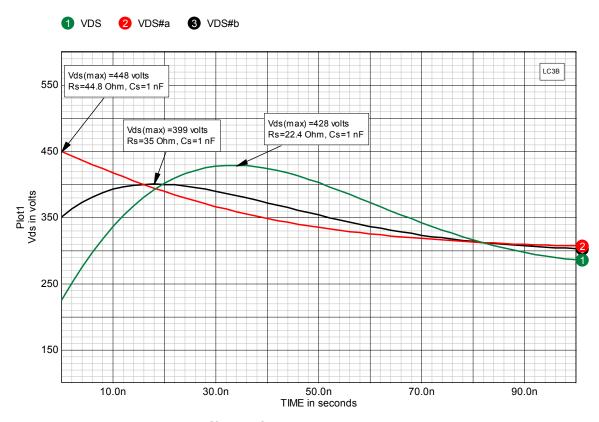

A detailed exposition can be found in McMurray<sup>[287]</sup>. For  $V_p/V_o$  values close to 2, Rs optimum will be close to  $Z_o$ . However, it is more common to have Vp/Vo < 1.4 which moves the optimum value for Rs above 1.5  $Z_o$ . Choosing Rs = 1.5  $Z_o$  is usually a good starting point.

Using the values in figure 3-15,  $Z_o$  = 22.4 Ohm. Experimentally we found the optimum value for Rs = 35 Ohm, so Rs = 1.6  $Z_o$ . In this case Vp/Vo =1.3.

The effect of different values for Rs on Vp is shown in figure 3-11.

Figure 3-11, effect of small changes in Rs on Vp.

As the waveforms show, the initial choice of value for Rs is not critical. Choosing Rs in the range of  $Z_o$  to  $2Z_o$  will give a well damped waveform but the optimum value, from the point of view of minimum  $V_p$ , will usually be somewhere in-between.

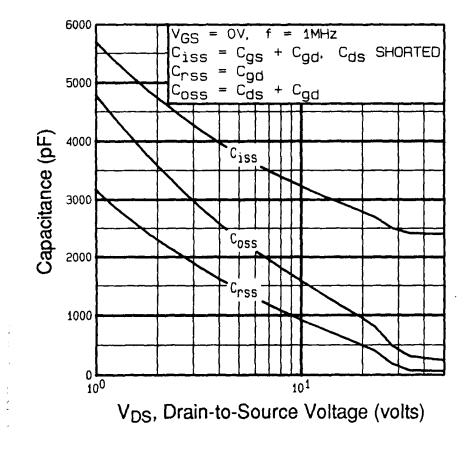

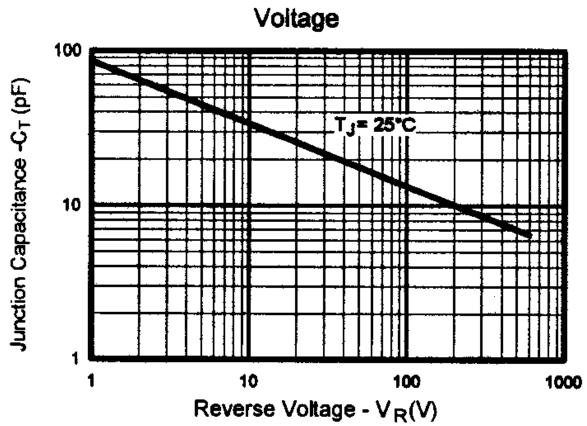

It may be disturbing to only guess at the optimum value of Rs when it is possible to compute an exact value<sup>[287]</sup> in an idealized situation. The reason we don't bother becomes clear when we move to a more realistic circuit where the output capacitance of the switch (Coss) is added as shown in figure 3-12.

Figure 3-12, circuit with Coss added.

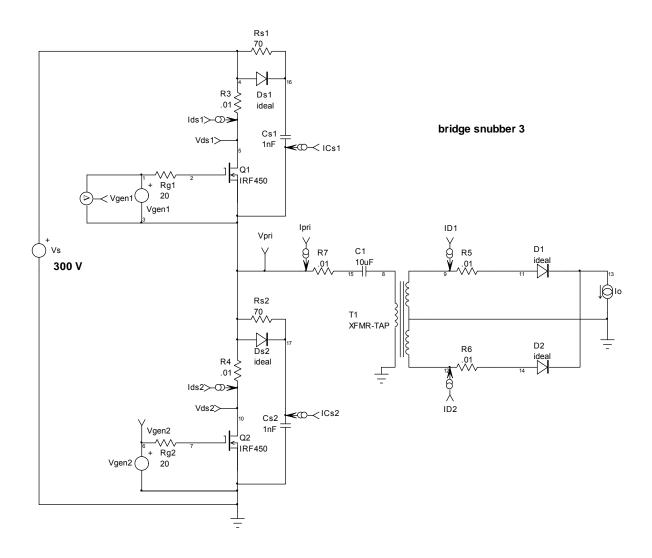

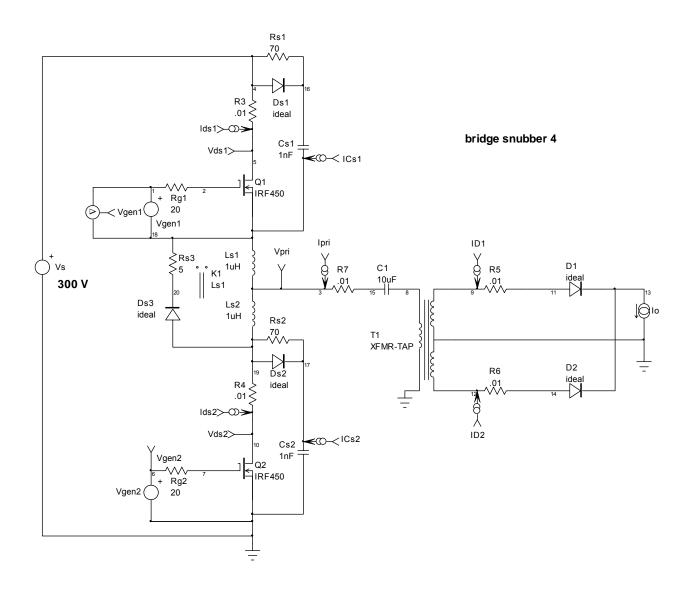

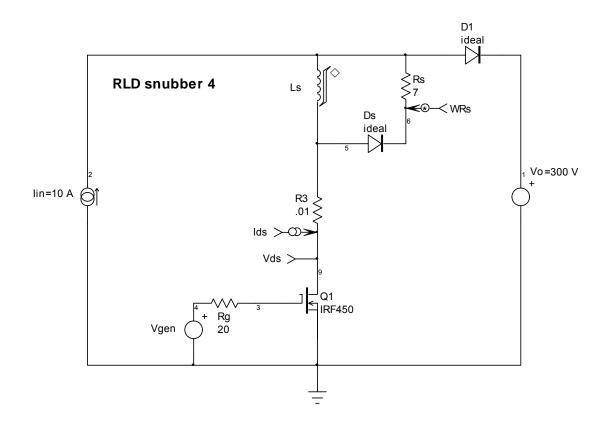

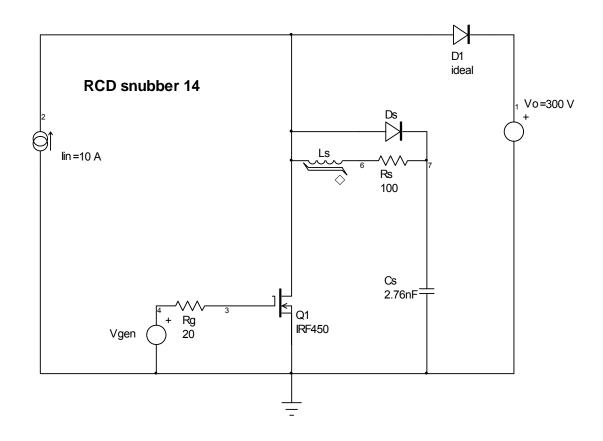

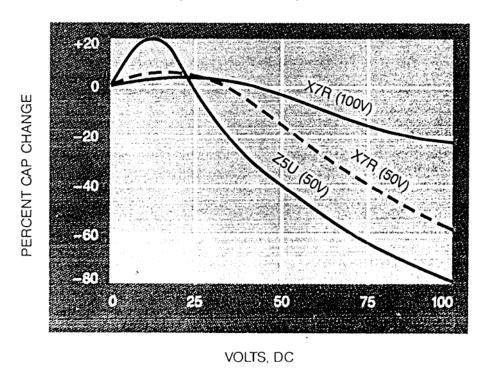

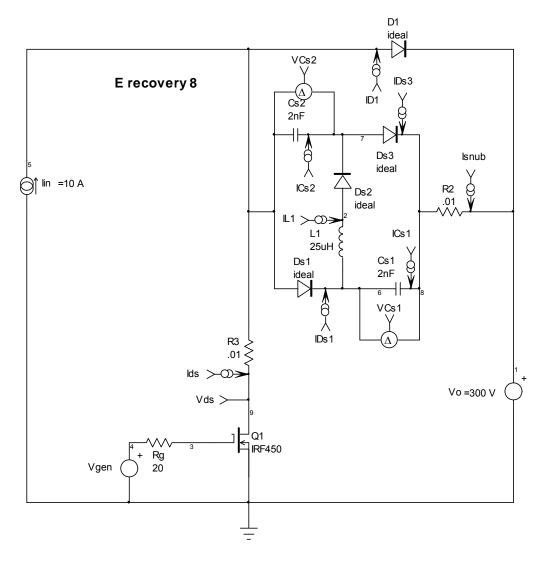

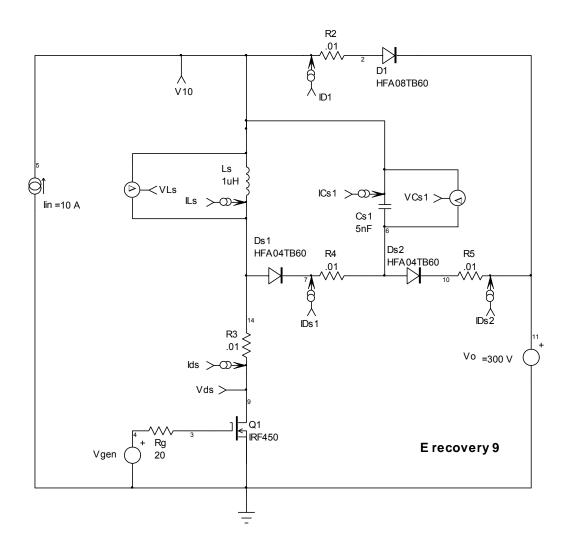

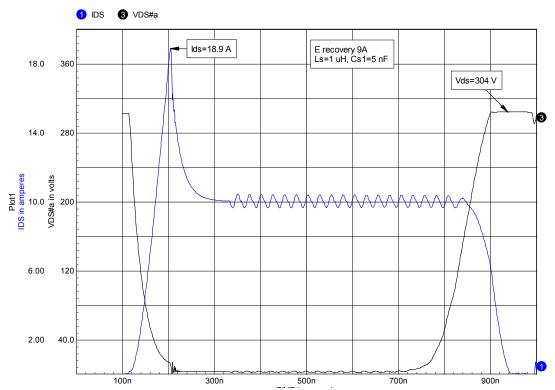

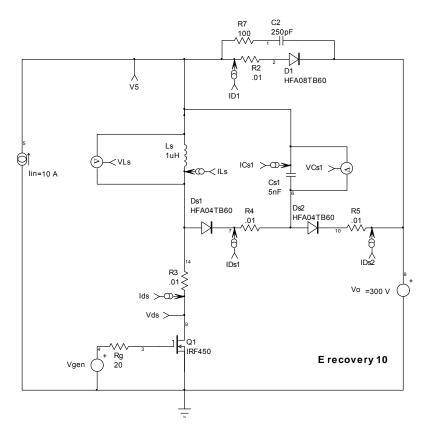

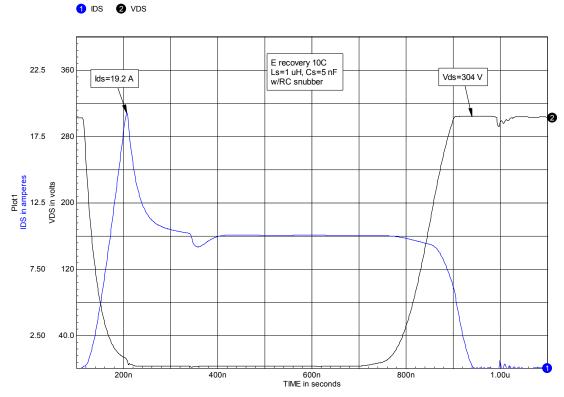

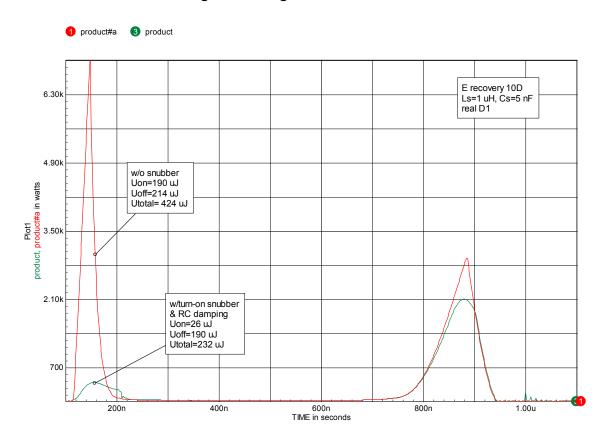

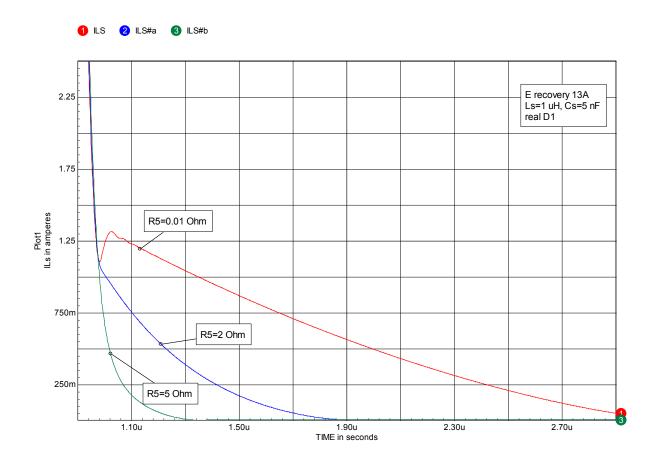

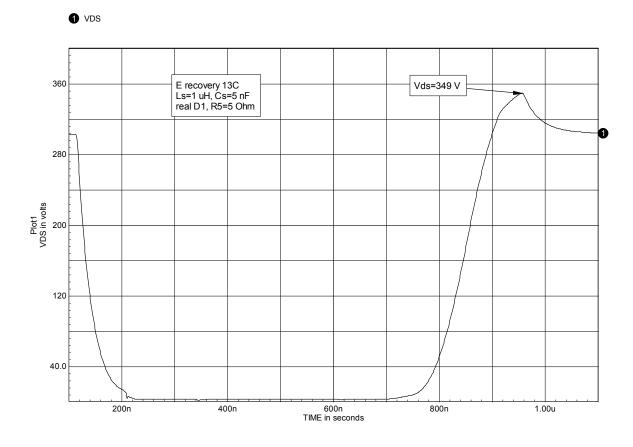

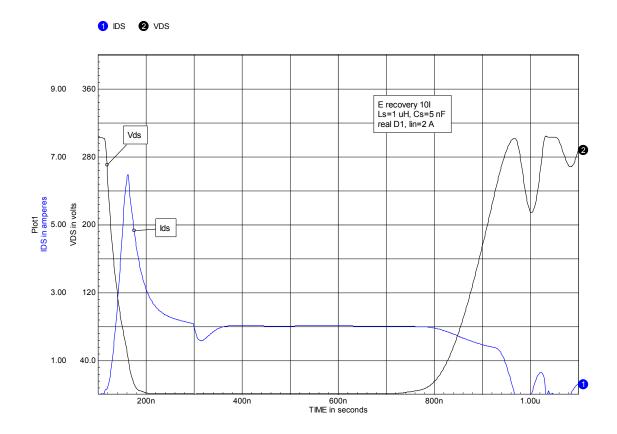

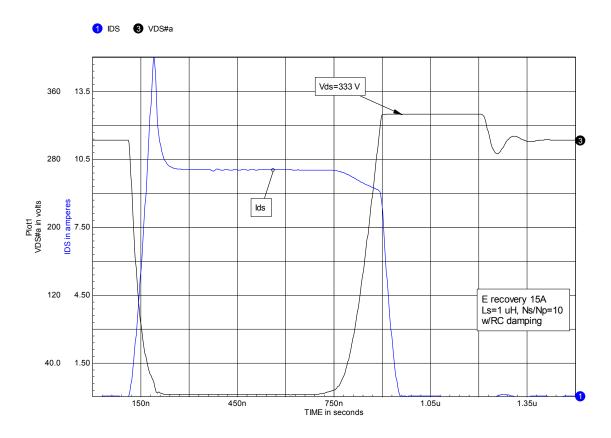

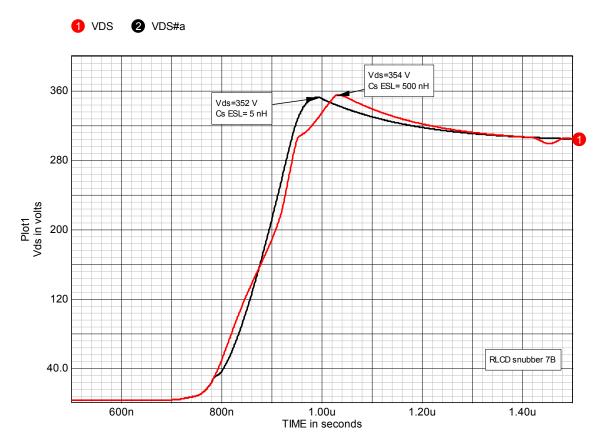

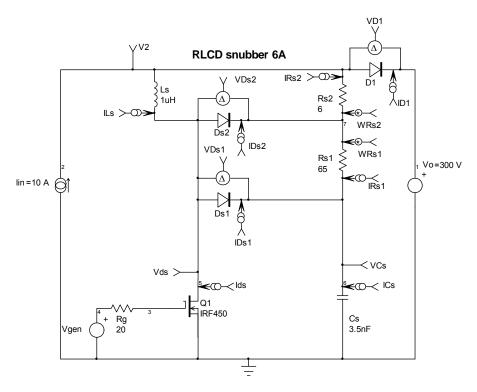

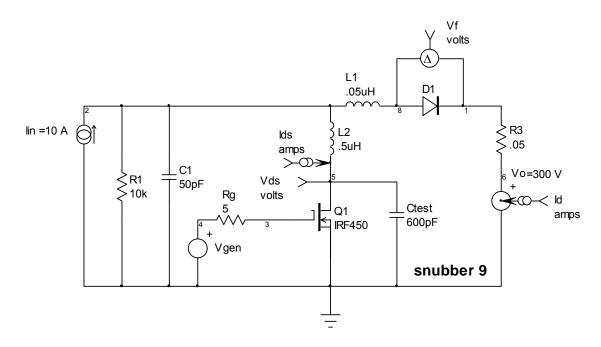

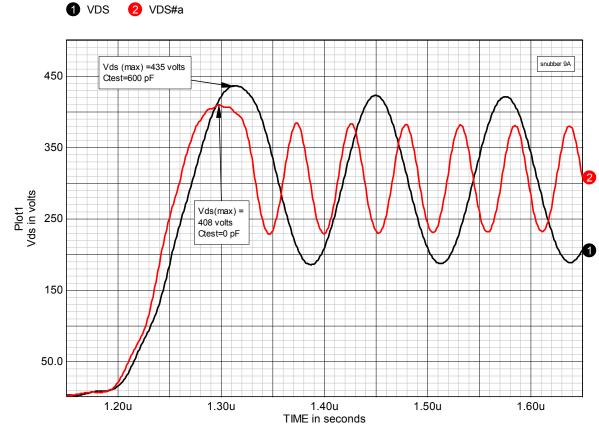

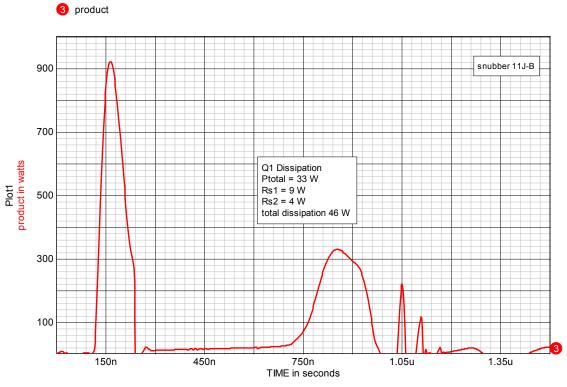

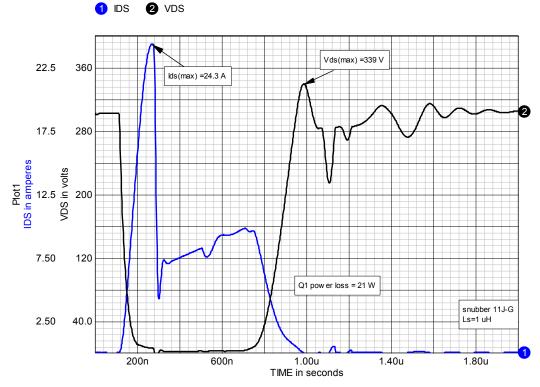

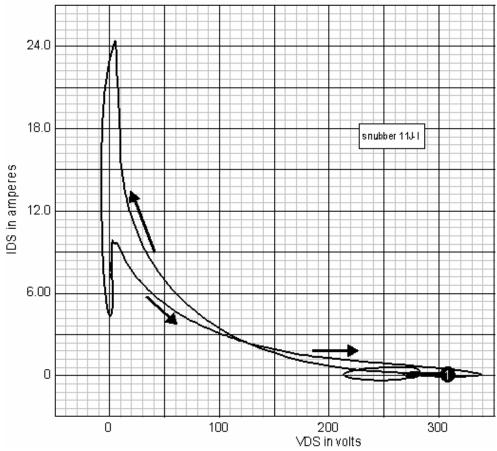

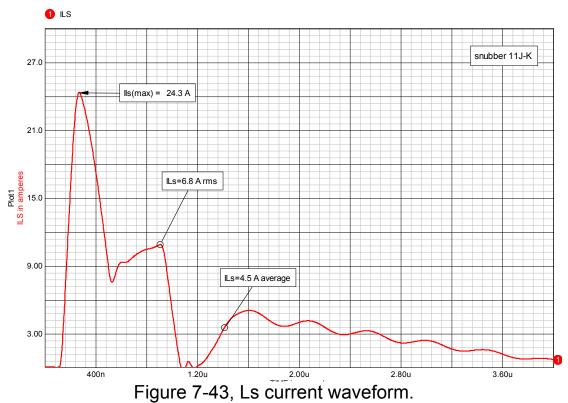

The effect of Coss on the Vds waveforms is shown in figure 3-13. With Rs= 35 Ohm, Cs = 1 nF and Coss = 0, Vp = 399 V. However, with the current values for Rs and Cs, Vp is now 489 V, an increase of 90 V! Coss has a profound effect on Vp because it reduces the effective damping in the circuit. We can vary Rs and will find the optimum value is about 29 Ohm. But Vp is still 482 V. If we want to reduce Vp further we will have to increase the value of Cs. In this example Cs  $\approx$  3 x Coss. The typical range for Cs is 3 to 10 x Coss. This is discussed further in chapter 7 (figure 7-11).